垂直线Fan-Out封装技术实现超薄移动存储器封装

半导体封装技术需要满足移动应用对更小尺寸和更高性能的需求。传统的细间距球栅阵列封装(FBGA)在厚度降低方面已经达到物理极限,即使将各个组件的尺寸都降低到临界点也难以进一步突破。扇出型晶圆级封装(FOWLP)技术通过消除有机基板,提供了设计灵活性和优异的电气性能,成为一个可行的解决方案。SK海力士在此基础上开发了一种名为垂直线扇出型封装(VFO)的新型封装方式,将FOWLP技术的优势与独特的垂直互连结构相结合,在保持稳健性能的同时实现了更薄的封装厚度[1]。

1.VFO封装的结构设计

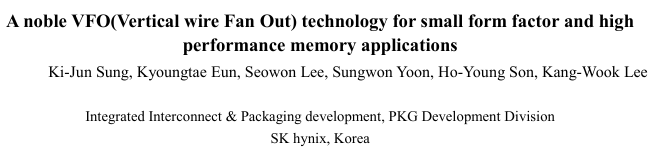

VFO封装采用了与传统存储器封装方案明显不同的结构设计。该技术的核心在于使用垂直线连接重构堆叠的芯片,并配合多层重布线层(RDL)来建立电气通路。这种架构从根本上区别于传统FBGA封装,用基于聚合物的RDL取代了有机基板,在不影响功能的前提下大幅降低了封装高度。

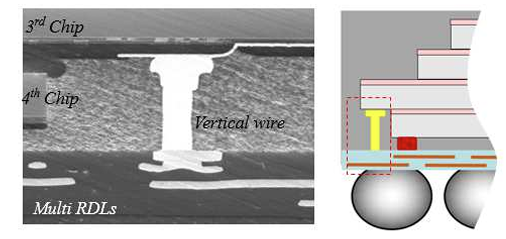

图1:VFO封装的示意截面图,展示了包括顶部封胶、芯片层、垂直线、多层RDL和焊球在内的关键结构元素。

该技术的演示载体包含8颗移动存储器芯片,采用2个着陆点、4层堆叠的配置,集成在单个封装内。垂直线作为关键的互连元件,沿着每颗芯片的外围焊盘排列,在堆叠芯片与下方的RDL网络之间建立电气连接。这种垂直互连策略对于空间受限的存储器应用特别有效。

2.制造工艺与集成流程

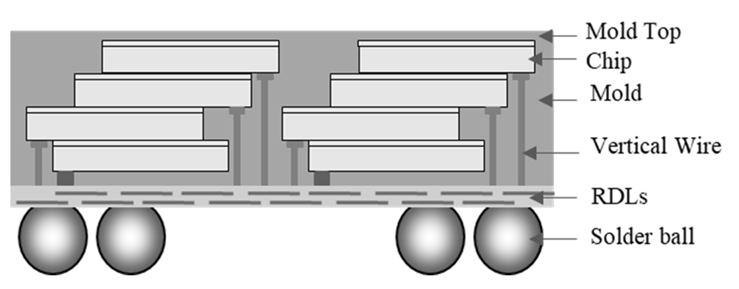

VFO的制造工艺采用基于FOWLP方法的RDL后置方式,进一步降低了封装高度,同时简化了工艺步骤。制程序列首先进行垂直线的形成,在多颗芯片堆叠完成后,沿着外围焊盘战略性地布置这些互连结构。芯片和垂直线的组合体经过环氧树脂封装,形成稳定的统一结构。

图2:(a)多芯片重构的近景视图,显示垂直线互连结构;(b)取代传统基板结构的多层RDL。

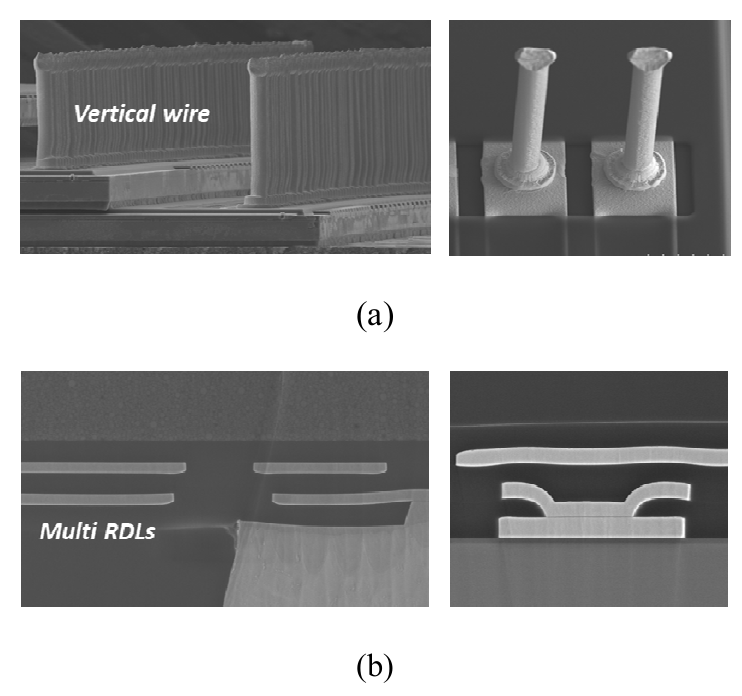

封装完成后,通过标准的背面研磨工艺去除多余的封胶材料,达到所需的厚度轮廓。随后的RDL制作采用聚合物介电层和电镀铜互连来形成布线层,有效替代了传统的有机基板。这种方法在占用更少垂直空间的同时提供了必要的电气通路。最后的制造步骤是通过回流工艺形成焊球,完成封装组装。截面检查显示,垂直线与多层RDL之间的连接质量良好,证明了这种互连方案的可靠性。

图3:扫描电子显微镜下VFO封装的截面图像,清晰显示了垂直线将堆叠芯片连接到多层RDL的情况。

3.封装厚度的大幅降低

与传统FBGA封装相比,VFO技术实现了显著的厚度降低。通过实施20微米的顶部封胶和三层RDL结构,总封装厚度从690微米降低到500微米,减少了27%。这一成果源于封装堆叠中多个因素的改进。RDL结构仅为40微米,而FBGA封装中使用的基板厚度为100微米。通过优化芯片堆叠和封装工艺,封装本体厚度从280微米降低到240微米。最显著的改善是顶部封胶厚度从110微米大幅降低到仅20微米,这得益于RDL后置方法在加工过程中保护了精细的垂直线结构。

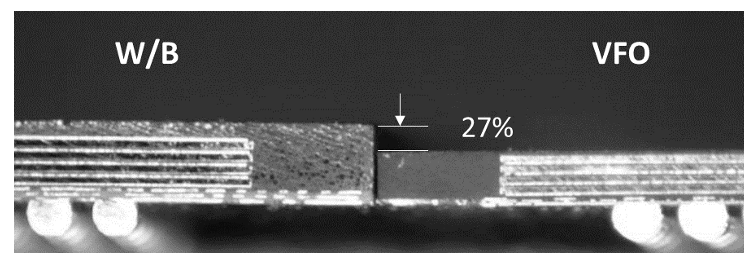

图4:并排对比显示传统FBGA(左)与VFO(右)封装的厚度差异,说明整体高度降低了27%。

4.机械性能与翘曲控制

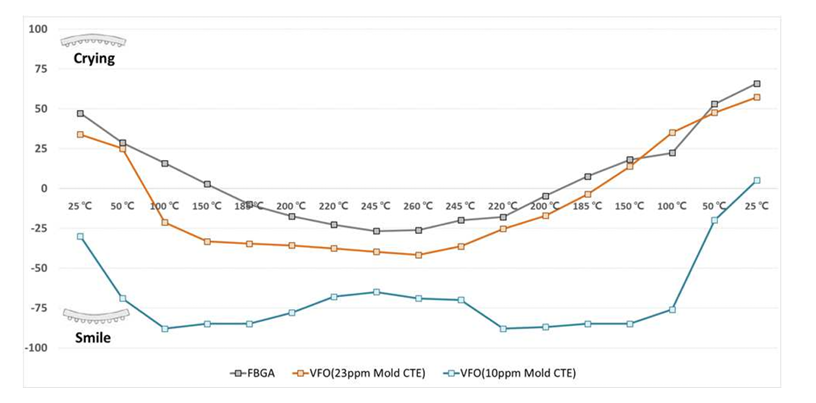

封装翘曲对组装可靠性特别是焊点质量具有重要影响。VFO技术通过精心选择材料和结构设计来应对这一挑战。使用阴影莫尔法进行翘曲表征,评估了两种具有不同热膨胀系数(CTE)的封胶材料。高CTE材料(A型)在室温(30°C)下表现出超过34微米的哭泣状翘曲,在回流温度(260°C)下为负42微米的微笑状翘曲。相比之下,低CTE材料(B型)在室温下的翘曲差异为60微米,在回流温度下为30微米。

图5:翘曲行为比较,显示FBGA和VFO封装中两种不同封胶材料(A型和B型)随温度变化的变形曲线。

A型封胶材料表现更优,其翘曲趋势与FBGA仅有轻微差异。这种行为源于RDL材料与封胶材料之间紧密匹配的CTE,最小化了热膨胀差异和由此产生的机械应力。通过材料工程控制翘曲的能力确保了组装过程中焊点形成的可靠性。

5.热管理特性

热性能分析采用符合JESD 51-2和51-9标准的仿真方法,在静止空气条件下进行结点到环境的测试。在环境温度设定为25°C、功率耗散为1瓦的条件下,VFO封装的结点温度达到49.2°C,热阻为每瓦24.9°C。相比之下,FBGA封装的结点温度为49.9°C,热阻为每瓦24.2°C。虽然VFO封装由于更薄的轮廓导致热质量减少而显示出略高的热阻,但这种差异很小,对于移动应用来说是可以接受的,因为热设计范围通常能够容纳这种变化。

6.优异的电气性能

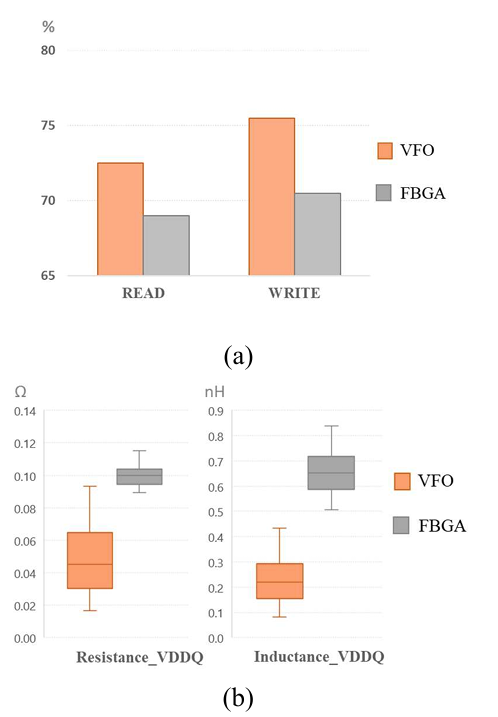

电气特性评估集中在封装叠层(PoP)配置中的信号完整性(SI)和电源完整性(PI),存储器封装位于顶部,应用处理器封装位于底部。信号完整性分析使用基于LPDDR DRAM规格的发射器和接收器驱动器模型。通过优化的RDL设计,VFO技术在读取操作期间实现了4.9%的眼图开口改善,在写入操作期间提高了6.6%,相较于FBGA封装有明显优势。这些更大的单位间隔开口提供了更宽的设计裕度,能够支持更高的工作速度,这对带宽需求大的移动应用至关重要。

图6:(a)信号完整性比较,显示VFO在读取和写入操作中相对FBGA改善的眼图开口百分比;(b)电源完整性测量,展示VFO设计降低的电阻和电感值。

电源完整性测量显示了更显著的优势。与FBGA相比,VFO封装中VDDQ电源网络的电阻和电感分别降低了约55%和64%。这些改善源于RDL方法固有的设计灵活性,能够为电源和地分配网络实现更短的布线长度。寄生电阻和电感的降低直接转化为改善的电源传输网络阻抗,即使在现代高速存储器操作典型的快速电流瞬态期间也能支持稳定的电压供应。

7.可靠性验证

按照JEDEC标准进行的综合可靠性测试验证了VFO封装在苛刻环境条件下的结构完整性。测试项目包括温度循环测试条件B(TCB),温度在负55°C和125°C之间变化1000个循环。此外,110°C、85%相对湿度、168小时的无偏高加速应力测试(uHAST)以及130°C、85%相对湿度、施加电压、96小时的HAST评估了耐湿性能。150°C、1008小时的高温存储(HTS)测试评估了长期热稳定性。

图7:可靠性测试后的截面分析,显示垂直线与RDL层之间的互连保持完好,没有出现分层或开裂失效。

测试载体成功通过了所有可靠性测试,RDL结构中没有出现分层,垂直线连接处也没有接头开裂。关键互连部位从垂直线到RDL的截面失效分析证实了结构完整性,验证了制造工艺的稳健性和材料系统的兼容性。这些结果表明,尽管VFO封装具有新颖的架构和超薄轮廓,仍能保持与成熟封装技术相当的可靠性标准。

8.技术特点与应用前景

VFO技术在移动应用存储器封装方面取得了明显进展,同时解决了尺寸小型化和性能提升的双重需求。相比传统FBGA封装27%的厚度降低直接支持了更纤薄的移动设备设计,而改善的电气特性——读取性能提高近5%、写入性能改善超过6%——满足了更高的带宽要求。可控的翘曲行为确保了可靠的组装工艺,而适度的热阻增加在典型移动热设计约束范围内是可以接受的。更重要的是,全面的可靠性验证确认了这些优势并未牺牲封装耐久性。随着移动设备继续向更薄轮廓和更高性能需求演进,VFO技术为下一代存储器封装提供了一个经过验证的平台,在尺寸、速度和可靠性之间取得了良好的平衡。

参考文献

[1] K.-J. Sung, K. Eun, S. Lee, S. Yoon, H.-Y. Son, and K.-W. Lee, "A noble VFO(Vertical wire Fan Out) technology for small form factor and high performance memory applications," in 2023 IEEE Electron Devices Technology & Manufacturing Conference (EDTM), Seoul, Korea, Mar. 2023.

来源:《逍遥设计自动化》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。