底部填充工艺如何为芯片封装“强基固本”

一、概述

随着芯片向小型化、轻薄化和高密度集成方向发展,倒装芯片技术凭借其信号路径短、散热佳、电性能优越等优势,成为先进封装的主流方案。然而,该技术中芯片与基板间的热膨胀系数差异会引发应力,威胁焊点可靠性。为此,行业普遍采用底部填充工艺,通过环氧树脂填充间隙,以分散应力、保护焊点,并通过添加二氧化硅等材料优化其力学与防潮性能。

当前底部填充主要包括流动式、非流动式、模压式及晶圆级等工艺路线。随着芯片集成度持续提高、凸块间距不断缩小、无铅焊料普及,工艺在效率、材料选择与可靠性方面面临新挑战。本文将重点阐述底部填充工艺的关键流程、改进方法、研究进展及现存挑战。

二、工艺定义与核心价值

倒装芯片的底部填充工艺,绝非简单的“打胶”操作。它是一种精密、关键的可靠性工程技术,其核心使命是解决微电子封装中最根本的机械可靠性矛盾,是确保芯片在复杂多变的工作环境中长期稳定运行的“定海神针”。

1)工艺定义:微观世界的精密“灌注”

底部填充工艺,是指在已完成电气互连的倒装芯片(Flip Chip)与承载它的基板(Substrate)之间的、仅有数十至上百微米的狭窄间隙内,精确注入一种特制的液态高分子材料(通常为改性环氧树脂)。该材料在表面张力和毛细作用的驱动下,自动流遍整个芯片底部区域,包裹每一个微小的焊球(Solder Bump),随后通过加热固化,形成一层坚固、致密的固态高分子保护层。这层“人工骨骼”将芯片、焊点和基板牢固地结合成一个刚柔并济的整体结构。

2)核心矛盾:热膨胀系数失配——焊点的“阿喀琉斯之踵”

这项工艺之所以不可或缺,源于倒装芯片封装中一个与生俱来的物理困境——材料间的热膨胀系数(CTE)严重失配。

· 材料属性对比:

1.芯片:由单晶硅制成,CTE极低,约为 2.5 ppm/°C,热胀冷缩程度微小。

2.有机基板:常用FR-4或BT树脂等材料,CTE较高,约为 16-20 ppm/°C,对温度变化更为敏感。

3.焊球:通常为锡基合金,CTE约为 25 ppm/°C,其机械强度相对有限。

· 失效机理:

当电子设备工作时(如手机通话、处理器运算),芯片温度会反复升降。每次温度循环,由于CTE的巨大差异,基板的膨胀和收缩幅度远大于芯片。这种不协调的形变,导致连接二者的数百乃至上千个微型焊球,被反复地拉伸、压缩、扭曲,承受着周期性的高剪切应力。经历成千上万次这样的疲劳载荷后,微小的裂纹首先在最脆弱的焊点颈部或界面处萌生,并逐渐扩展,最终导致电气连接开路,设备功能失效。这是倒装芯片封装最典型的可靠性失效模式——热机械疲劳失效。

3)核心价值:从“应力集中点”到“应力分布层”的革命

底部填充胶正是为解决这一根本矛盾而设计的“机械工程师”。其价值体现在精妙的应力重分布上:

· 材料设计的智慧:优质的底部填充胶经过精心配方,其固化后的CTE通常在 30-50 ppm/°C 之间。这一数值介于芯片与基板之间,起到了梯度过渡的作用,有效缓和了形变差。

· 力学角色的转变:固化后的胶体具有高模量和高韧性。它如同一个坚固的“应力桥”和“缓冲垫”,将原本由焊点独自承担的、集中的剪切应力,大部分吸收并分散到整个胶层和更大的粘接面积上。焊点的主要功能从而从“承受机械应力”回归到更专一的“保证电气连通”。

· 可靠性飞跃:

经过底部填充保护的倒装芯片组件,其焊点的抗热疲劳寿命可以实现数量级的提升——通常可提高10倍乃至数十倍。这使得电子产品能够承受更严苛的环境温度变化(如汽车电子从-40°C到125°C的循环)、更频繁的功率循环以及日常使用中的机械振动与冲击。

总结而言,底部填充工艺的本质,是通过引入一种精心设计的复合材料,系统性地管理并解决由材料物理特性差异引发的可靠性风险。它不再是可选的后道工序,而是实现高密度、高性能、高可靠倒装芯片封装的必由之路和核心技术保障,直接决定了最终产品的品质与寿命。

三、工艺制造技术

1)模压式底部填充工艺

模压式底部填充工艺是一项旨在优化倒装芯片封装效率的集成技术,它将传统的底部填充与塑封合二为一,其核心优势与特点可归纳如下:

1.工艺核心:采用改性的环氧树脂模塑料作为填充材料,不仅能填充芯片与基板间的微间隙,还能一次性完成对整个芯片的塑封,从而将两个独立的工序合并,显著缩短了整体工艺时间。

2.材料特性:所使用的改性环氧模塑料中通常添加了高比例(如质量分数80%)的二氧化硅填料。这种配方使其在固化后具备与焊点、基板相匹配的低热膨胀系数,确保了封装结构在热循环下的机械可靠性。

3.关键挑战与解决方案:该工艺的主要技术难点是,在芯片间隙与凸块间距不断缩小的趋势下,如何避免填充过程中因流动阻力大而产生空气残留(空洞)。为此,业界普遍采取两项关键改进措施:

· 模具设计优化:采用带有排气设计的专用模具。

· 工艺辅助技术:引入真空辅助注塑技术,在填充时抽真空以减少空气滞留。研究已证明,结合使用细粒度填料的胶料与真空技术,可实现对极小间隙(如小于8微米)的可靠填充。

总结:模压式底部填充工艺通过材料与工艺的集成创新,在保证可靠性的前提下,有效提升了高密度倒装芯片封装的效率,是应对先进封装微型化挑战的重要解决方案之一。

模压式底部填充工艺流程

2)晶圆级底部填充工艺

晶圆级底部填充工艺是一种在晶圆层级就完成底部填充胶涂覆的先进技术,旨在与表面贴装技术完全兼容,其核心特点如下:

1.工艺本质:该工艺属于非流动式底部填充的改进形式。其核心步骤是,在切割前,通过旋涂(针对液体胶)或真空层压(针对薄膜胶)的方式,将底部填充胶预先、均匀地涂覆在整个晶圆表面。

2.流程与优势:涂胶后的晶圆经半固化(液体胶)或直接(薄膜胶)后,被切割成单颗芯片。这些已自带底部填充胶层的芯片,可直接用SMT设备进行贴装与回流焊接。此流程无需额外的点胶和固化步骤,能显著缩短工艺时间、降低成本,且与后端SMT产线高度兼容。

3.技术关键:工艺成功的关键在于对材料与过程的精密控制:

· 材料特性:胶体需在半固化态具备良好的储存稳定性和机械强度以利于划片,同时在回流焊时又能重新熔融流动,以完成焊点润湿和最终固化。

· 涂覆质量:必须确保填充胶能均匀、完整地覆盖晶圆表面,特别是要填满凸块形成的微台阶,任何覆盖不良都可能导致后续分层失效。

· 工艺参数:尤其是真空层压的压力、温度与时间,对薄膜胶的附着质量至关重要。

4.在三维封装中的应用:随着芯片向三维堆叠等更高密度封装发展,填充间隙变得极窄(如<15μm),传统流动式填充面临挑战。WLUF工艺因其在晶圆级实现均匀、超薄胶层的能力,成为三维/异质集成封装的理想选择。通过将其与非流动式填充和热压键合工艺相结合,已成功实现了对超窄间隙、超细间距微凸块器件的可靠填充。

晶圆级底部填充工艺流程

3)流动式底部填充工艺

好的,已将您提供的关于流动式底部填充工艺的内容整合、缩写并分点如下:

流动式底部填充工艺是应用最广泛的传统底部填充技术,其核心是利用毛细作用驱动胶体填充芯片与基板间的间隙。其核心内容可从工艺流程、材料体系和工艺优化三个方面进行概述:

1、工艺流程

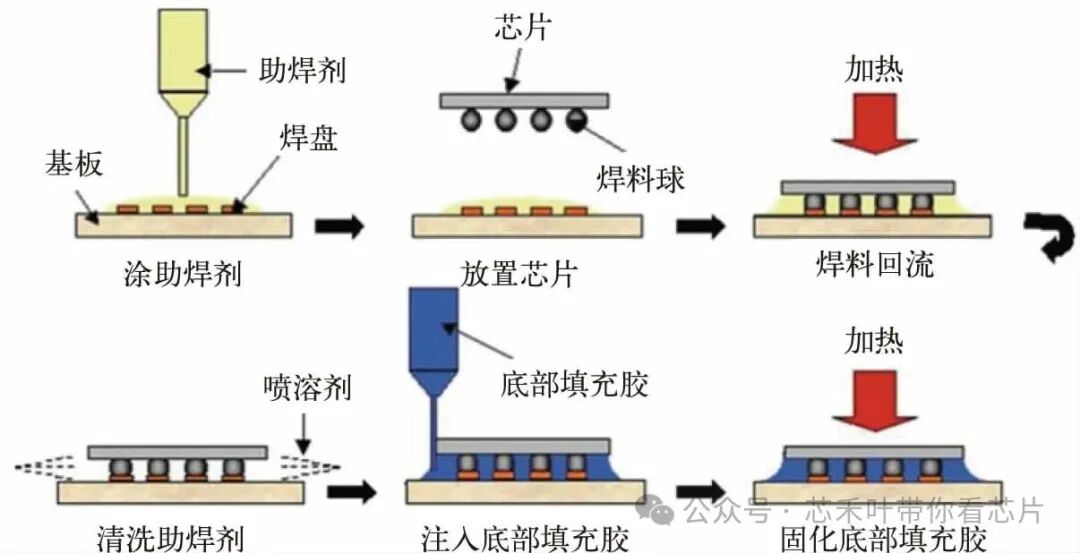

1.步骤:在芯片与基板完成焊接(使用助焊剂后需清洗)后,沿芯片边缘点入液态填充胶。胶体在毛细力作用下自动流入并填满间隙,最后经加热固化,将三者结合为一体。

2.关键影响因素:

· 点胶路径:不同的点胶方式(如单边、L形、U形)会显著影响胶体的流动路径、填充时间及空洞形成风险,需根据封装设计进行仿真与优化。

· 清洁度:焊接后残留的助焊剂是主要污染源,会阻碍胶体流动并导致固化后产生空洞,严重影响产品可靠性。

2、材料体系

典型的流动式底部填充胶是一种由液态环氧树脂与无机填料组成的复合材料:

1.有机基体:以环氧树脂为主,辅以固化剂形成交联结构,并加入催化剂以调节工艺时间与固化速度。

2.无机填料:主要添加微米级二氧化硅,用以降低固化后胶体的热膨胀系数、提高模量并减少吸湿性。研究表明,适量添加纳米级二氧化硅可进一步提升填充效率与可靠性。

3.功能助剂:为优化性能,常加入黏合促进剂、增韧剂和分散剂等,以改善混合均匀性并增强最终机械性能。

3、主要挑战与优化方向

填充速度慢(尤其是面对细间距、大尺寸芯片时)及空洞风险是工艺的主要瓶颈。针对性的优化措施包括:

1.改善流动:预热基板以降低胶体粘度,从而加快填充速度。

2.减少空洞:彻底清除助焊剂残留,并选用与其相容性更好的底部填充胶。

3.工艺优化:采用三段式等优化固化程序以消除微气孔;引入超声波振动辅助技术,利用声波驱动效应提高胶体流速。

4.设计优化:从封装设计源头入手,优化凸块的形状与排布,可有效缩短填充时间并减少空洞。

总结:尽管存在填充不完全和产生空洞的风险,但凭借其操作简单、与各类材料及封装设计兼容性好的优势,流动式底部填充工艺在实际生产中仍被广泛应用。

流动式底部填充工艺流程

来源:《芯禾叶带你看芯片》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。