使用电镀和湿法种子层蚀刻制造细间距Cu-Sn微凸点(上)

与需要复杂的化学机械抛光(CMP)和表面预处理才能达到优良焊接效果的Cu-Cu热压键合技术相比,Cu-Sn-Cu瞬态液相(TLP)键合技术可以实现简单流程和低成本的焊接过程。在TLP焊接过程中,焊点bump会被加热至锡熔化状态,而铜则会迅速扩散进入熔融的锡中,在焊接温度和适当的压力下形成金属间化合物(IMCs)。铜-锡IMCs具有优异的电气性能、较高的机械强度,且其二次熔点远高于锡的熔点。因此,铜-锡TLP键合技术被广泛应用于三维集成领域。

随着对高带宽要求的增加,Cu-Sn bump diameter和 pitch应缩小以增加bump density。然而,由于Cu-Sn-Cu键和不使用CMP,且液态Sn在键合压力下膨胀,Cu-Sn的bump size和pitch相当大。例如,工业生产中Cu-Sn bump的diameter和 pitch分别为20~30um和45~60um。对于未来的应用,Cu-Sn bump的diameter需要缩小到5μm或更小。然而,micro bump具有较大的表面积与体积比率,并面临着一些不同于大bump的技术难题和特点。

第一个问题是wet etching对Cu seed layer造成的显著undercut。通常Cu-Sn bump是通过在光刻胶掩膜上进行electroplating工艺来制造的。molding下方的seed layer厚度通常介于100~500nm之间。Electroplating完成后,为了便于操作且成本较低,通常会采用wet etching工艺来去除c。然而,由于wet etching固有的各向同性特性,这种蚀刻液会同时侵蚀bump和Cu seed layer,从而导致bump根部出现undercut现象。由于undercut与bump直径的比例较小,对于大bump而言,undercut微不足道,但对于小bump而言则很严重。例如,1um的undercut仅为直径为20um的bump的10%,但约为直径为5um的bump的40%。

其次,在铜-铜热压键合工艺中所需的CMP(化学机械平坦化)在Cu-Sn TLP键合工艺中则非必要。通常施加键合压力以确保牢固接触、破除自然氧化层并加速IMC(金属间化合物)的形成。然而,在键合压力下,液态锡会向外溢出。这种锡的溢出限制了bump pitch的缩减,因为溢出的锡可能造成相邻bump间出现短路。

本文对wet etching与键合工艺进行了研究并优化,并展示了直径为5μm的bump的制造与键合过程。采用电镀技术来制造具有良好均匀性和高成品率的bump阵列。对seed layer的wet etching与dry etching进行了研究与比较。键合结果及电气测试表明,该工艺具有很高的可靠性和良好的电气性能。

1、实验

(1)Cu-Sn micrbump 电镀

通过电镀工艺进行Cu-Sn micrbump 制造。需要进行电镀的wafer置于阴极,而铜板和锡板分别用作进行铜电镀和锡电镀的阳极。晶圆和金属板被浸入含有特殊金属盐溶液的电镀液中。当施加直流电流时,铜或锡会从金属板中通过电化学氧化反应溶解于溶液中。随后,这些离子被输送到目标wafer上,并通过电化学还原反应沉积在seed layer上。

通过在400mm silicon wafer上采用热氧化工艺生长一层400nm的SiO2层。为了增强Cu seed layer与SiO2之间的附着力,需在SiO2表面沉积一层20nm的TiW层作为粘附层。随后,在TiW层上溅射一层100nm的Cu层作为电镀的seed layer。在seed layer上应用PR掩膜模,并形成孔径为5um、pitch为20um的图案。接着,通过施加直流电流进行连续的Cu和Sn电镀,以沉积Cu层和Sn capping layer。厚度为800nm的铜薄膜用于与bump键合。

按照化学计量比计算了Cu/Sn层的厚度,并额外增加了Sn层的厚度以补偿加热焊接过程中Sn的挥发。对于小直径器件而言,热回流无法改善bump的形态,因此实现良好的表面smoothness 和height uniformity颇具挑战性。

(2)seed layer刻蚀

在完成铜/锡层的电镀以及光刻胶掩膜的stripping后,应去除未被bump覆盖的100nm铜种子层和20nm TiW粘附层。移除种子层最常用的方法为wet etching,这种方法具有成本低廉且操作简便的优势。然而,wet etching固有的各向同性特性会导致bump根部不可避免地出现undercut现象。

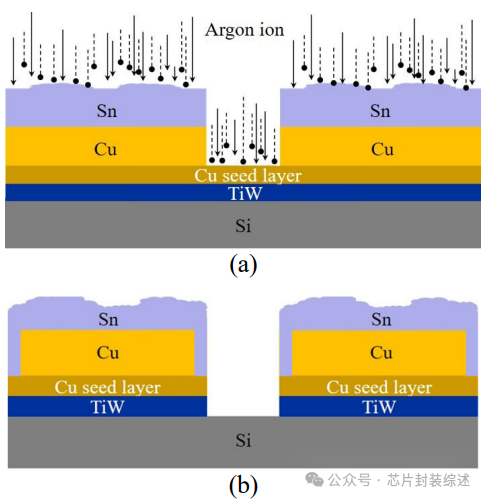

离子束蚀刻(IBE)具有较好的方向性,且不会造成横向刻蚀。因此,从理论上讲它适用于小型Cu-Sn bump,如下图所示。然而,由于IBE本身并无选择性,离子束也会对Sn进行刻蚀。干法刻蚀会导致温度升高和Sn熔化,从而造成Sn出现在bump侧壁上的情况。此外,人们还发现IBE会在Cu-Sn bump顶部形成类似草状的结构。

参考文献:[1] Shi Y , Wang Z , Wang Q ,et al.Fabrication of Fine-Pitch Cu-Sn Microbumps Using Electroplating and Wet Seed Layer Etching[J].2024 IEEE 10th Electronics System-Integration Technology Conference (ESTC), 2024:1-4.

来源:《芯片封装综述》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。