TSV键合工艺介绍

TSV 在制作完成后,为了实现与上下层芯片或衬底的信号连接,需要将 TSV 与 TSV、芯片和衬底相互键合,键合方式分为凸点键合和无凸点键合。制造凸点的主要工艺有焊锡凸点电镀、焊膏压印、铜柱凸点电镀和焊锡注模。混合键合可以替代凸点,实现 TSV 中 Cu-Cu 的无凸点键合。

1.焊锡凸点

随着制造微小凸点技术的成熟,电镀正成为一种流行的凸点制造方法。通过将晶圆放入镀槽中进行电镀,实现凸点制备。但是以电镀法制备凸点的工序相对复杂,改变焊料合金的成分相对较难,需要对镀液中各组成成分的含量进行控制,且镀液的稳定性较差。

图 4 展示了在不使用 PR 模具的条件下以直流电镀在铜塞上形成凸点的工艺步骤。对于非 PR 模具工艺, TSV 中的焊缝、空洞和不完全填充等缺陷会导致不规则凸点的形成。因此,TSV 的填充质量会直接影响到焊锡凸点的制备。

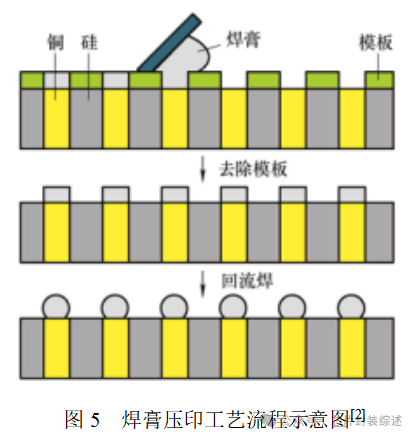

焊膏压印工艺是通过在 TSV上的细间距模板压印焊膏,然后回流焊,最终形成焊锡凸点,其工艺过程如图 5 所示。在焊膏压印中,为了形成无缺陷的凸点,需要特别注意基板表面状况、基板-模板比(模板开口尺寸,间距大小,模板厚度),压印速度和压力大小等各种参数。

2.铜柱凸点

铜柱凸点(Copper pillar bump, CPB)可替代传统焊料凸点,其结构和生产工艺与电镀焊料凸点类似,制造过程主要结合了光刻和电镀工艺。CPB 的制造过程如图 6 所示。CPB 工艺是通过电镀在 TSV 上形成一个较高的铜柱凸点,并在凸点的顶部镀上一层较薄的焊锡膜。与传统焊料凸点相比较,CPB 结构使得凸点中焊料的体积分数显著减小,而铜柱主要承担了大部分的支撑高度。

通过电镀法在 TSV 上形成焊锡凸点时,凸点间距通常在70~140 μm之间。但是,当间距小于70 μm时,在回流焊的过程中相邻焊点可能会发生桥接。通过 CPB工艺可以形成更小间距的凸点而不产生桥接,并且具有良好的散热性能和较高的机械屈服强度。在热处理过程中,由于金属原子的扩散,焊锡膜与铜柱的界面处会形成金属间化合物,严重影响互连可靠性。通过在铜柱和锡层之间添加镍层能有效缓解金属间化合物的生成,提高凸点互连可靠性。

焊锡注模(Injection moldedsolder,IMS)工艺又称铜柱上的焊锡注入,在这个过程中,熔化的焊锡金属从喷嘴尖端被挤出到铜柱上。IMS 的过程如图7 所示 。IMS 工艺包含以下步骤:在晶圆上形成种子层和 PR 样板、铜柱电镀、焊锡注入、PR 和种子层剥离。

3.混合键合

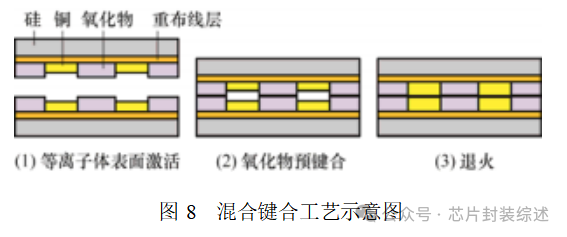

混合键合是一种实现介质层与介质层、金属与金属界面无缝隙键合的技术,其工艺过程如图 8 所示。在 TSV 键合中,介质层通常为 SiO2,金属通常为 Cu。 SiO2介质层为集成单元提供机械支撑与电气隔离,Cu-Cu 键合提供芯片间的垂直电气互连。对于 Cu 和SiO2混合键合结构,首先要得到具有亲水性、粗糙度小的待键合表面,然后进行直接键合,最后进行退火处理。退火在增强 SiO2-SiO2 键合强度的同时,也促进了 Cu 晶粒的生长和扩散以实现 Cu-Cu 键合。

4.键合工艺小结

表 4 总结了TSV 键合工艺的相关研究进展。通过电镀形成的焊锡凸点在回流焊后无裂缝产生,大小均匀。焊膏压印工艺的关键在于基板参数、压印速度和压力大小,能够形成晶圆级细间距焊锡凸点。相比于焊锡凸点,电镀铜柱凸点具有良好的散热性和高可靠性,并且不会发生桥接。焊锡注模工艺最大优点是能形成均匀、等高的凸点,弥补了因通孔内填充物高度不一致导致凸点高度不一致的问题。与凸点键合相比,混合键合简化了工艺步骤和键合结构,Cu 密封在无机介质层中,不需要凸点下金属层和底部填充物,提高了散热性能、电气性能、热机械可靠性和封装密度。

参考文献:[1]王美玉,张浩波,胡伟波,等.三维系统级封装(3D-SiP)中的硅通孔技术研究进展[J].机械工程学报, 2024, 60(19):261-276.

来源:《芯片封装综述》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。