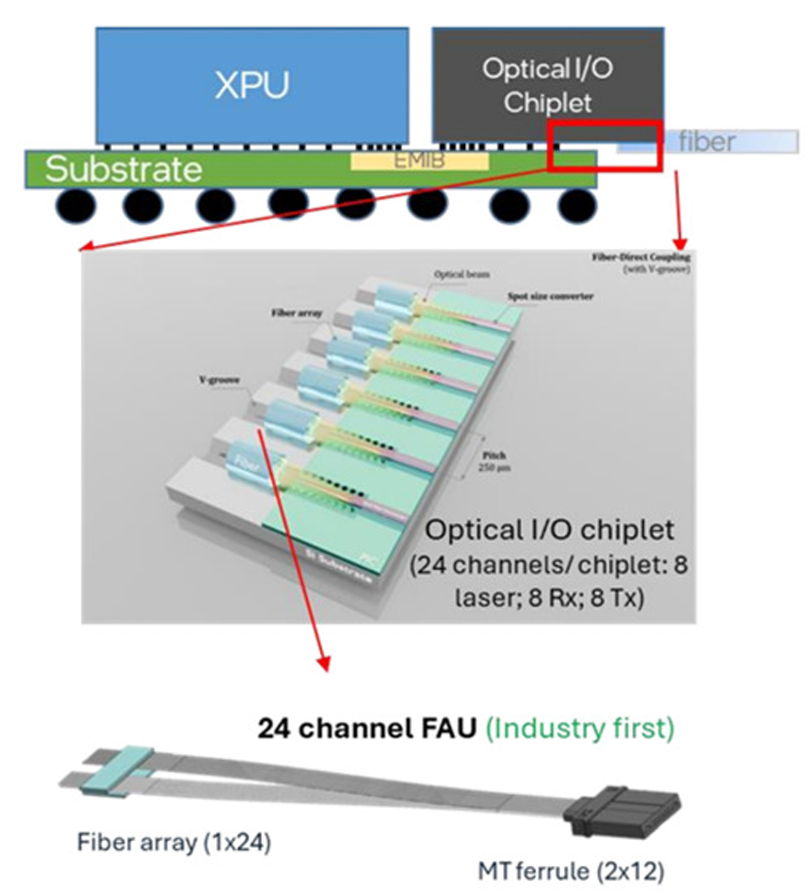

光电共封装异质整合技术解析

01 引言

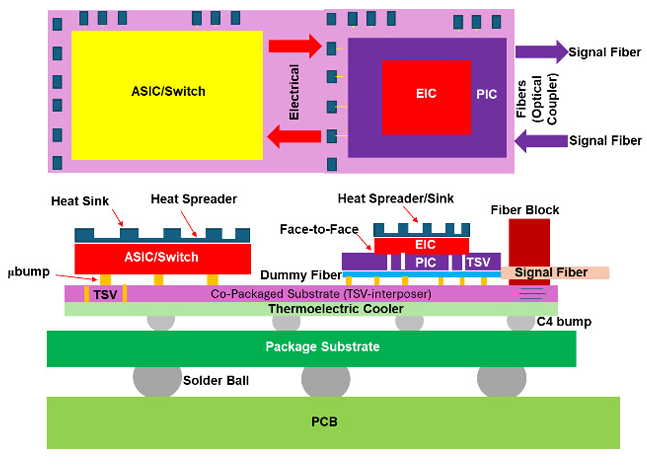

数据中心对于人工智能运算与高速网络的需求持续增长,传统可插拔光收发模块在功耗与带宽方面面临瓶颈。光电共封装(CPO)技术将光学引擎(包含光电子芯片 PIC)、电子引擎(包含电子集成电路 EIC)以及应用专用集成电路(ASIC)交换机整合于共同基板上,缩短电气接口长度,降低信号驱动能耗,减少延迟,提升整体电气效能。本文探讨 CPO 技术基础、发展历程,以及各种架构实现方式。

02 技术基础与元件组成

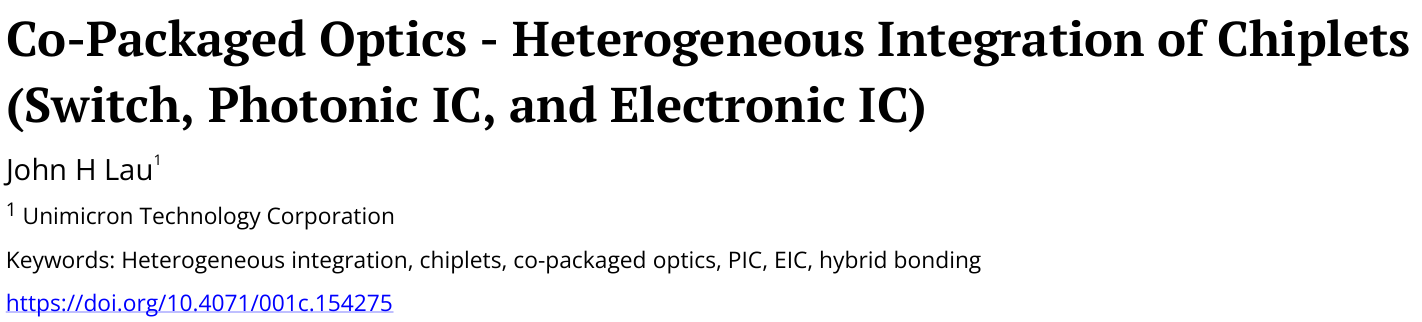

图 1:混合硅激光结构示意图,展示磷化铟(InP)光发射材料透过薄玻璃层接合于硅晶圆顶部,实现激光与集成电路于同一硅平台整合的混合技术。

光电元件包括产生、操控与侦测光线的组件,例如发光二极管(LED)、激光、光检测器(PD)等。硅基光电子技术将光学元件整合于硅芯片上,利用光信号取代传统电信号传输数据。此技术运用互补金属氧化物半导体(CMOS)制程于硅晶圆上制作波导、调制器及其他光学元件,并与电子线路并存。

二十年前,业界积极推动硅整合方案,Intel 等公司推广硅基光电子技术,将 PIC、EIC 与波导整合于单一硅芯片上。终极目标是将所有光电子与电子元件整合至单一硅芯片。然而近年来,成本考量促使产业转向将功能分割为较小 Chiplet,再于基板上整合。硅基光电子技术虽具备较佳效能与测试便利性,但成本较高且基础设施较为固定。Chiplet 方案则提供较低成本与更大弹性,但在效能与封装尺寸方面有所取舍。

03 从可插拔到共封装的演进

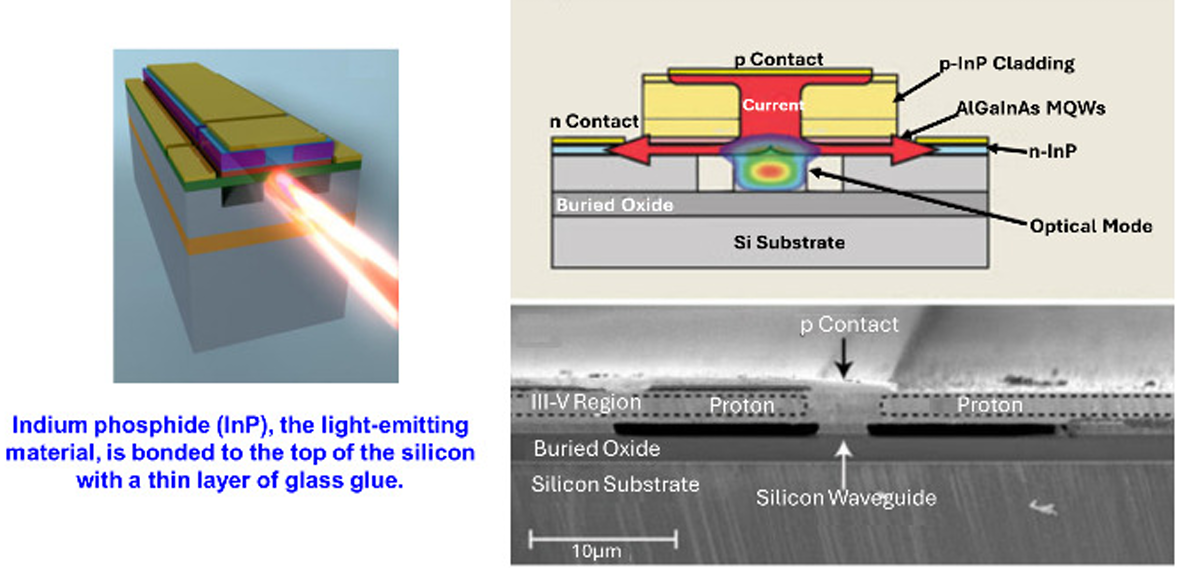

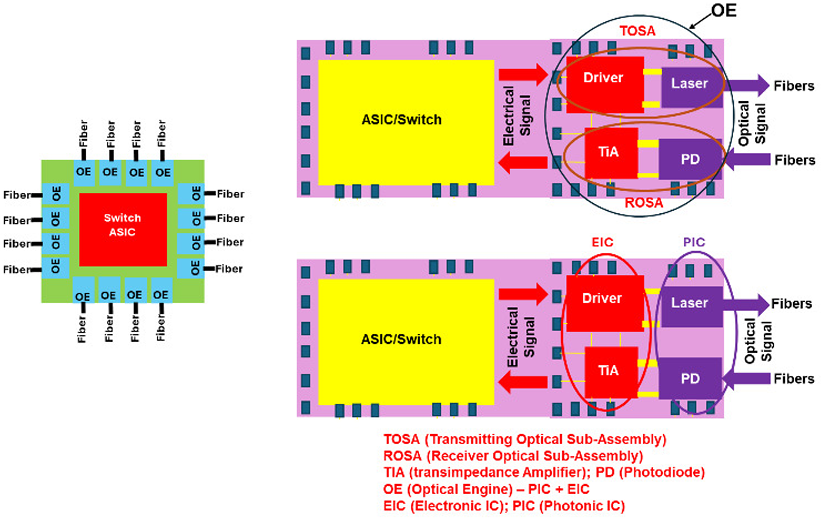

图 2:配置可插拔收发模块的数据中心架构,显示可插拔收发模块安装于印刷电路板边缘,ASIC 封装独立安装,代表 CPO 技术演进的起点。

数据中心包含交换机、路由器与存储方案等复杂网络,支援共享应用程式与数据传递。目前超过九成的收发模块采用可插拔式设计。这些装置包含发射光学次组件(TOSA)与接收光学次组件(ROSA)。TOSA 模块整合半导体激光二极管与激光驱动器,将电信号转换为光传输信号并耦合至光纤。ROSA 包含光检测器、透镜等光学接口元件、跨阻放大器(TIA)与被动电气接口,接收来自光纤的光信号并转换回电信号。

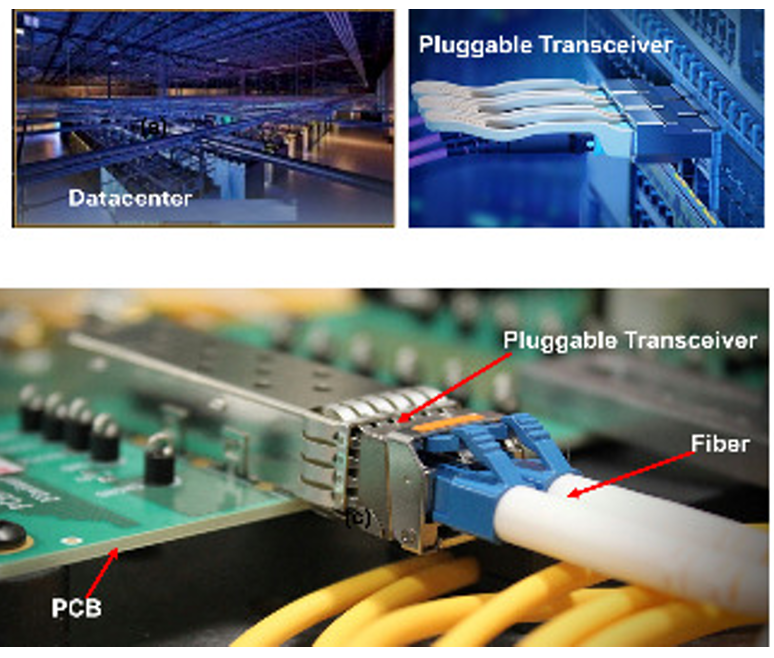

图 3:数据中心 CPO 架构示意,包含 TOSA、ROSA、PIC 与 EIC 元件,展示光收发模块整合于共同封装基板与 ASIC 交换机并列的未来配置,缩短互连距离并改善效能。

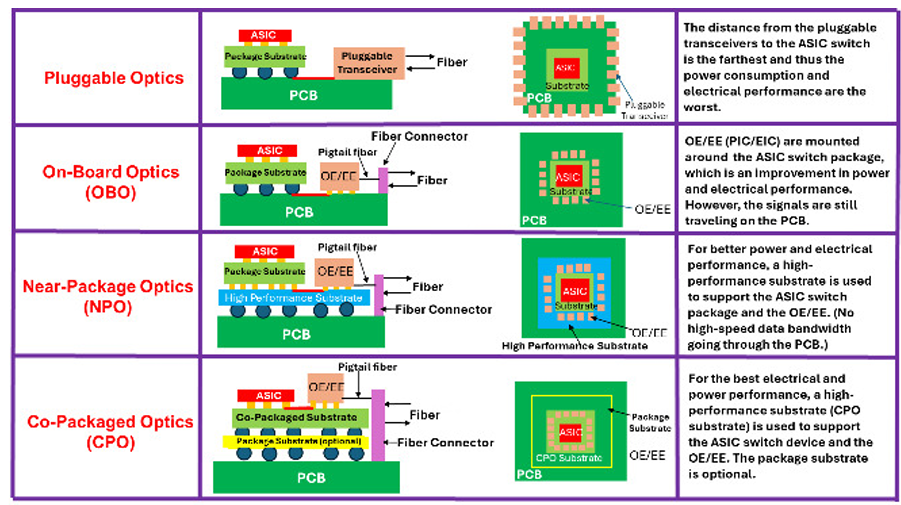

从可插拔光学到 CPO 经历数个中间阶段。可插拔配置中,收发模块安装于印刷电路板边缘,ASIC 封装独立安装于基板,造成光电元件与电气元件间距离最远,功耗与电气效能最差。2018 年起,板载光学(OBO)将光学与电子引擎安装于与封装 ASIC 相同的印刷电路板上,配置于 ASIC 四周。此配置缩短元件间距离,改善功耗与电气效能。

图 4:可插拔光学、OBO、NPO 与 CPO 架构比较图,展示从可插拔(距离最远)经 OBO 与 NPO 到 CPO(距离最短)的演进,相应地改善功耗与电气效能。

2020 年起,近封装光学(NPO)将光学与电子引擎与封装 ASIC 并列于高性能基板而非印刷电路板。根据光互连论坛(OIF)规范,NPO 应用允许 ASIC 与光学元件间距离达 150mm,通道损耗限制于 13dB。此架构消除高速数据透过印刷电路板传输,达成较佳功耗与电气效能。

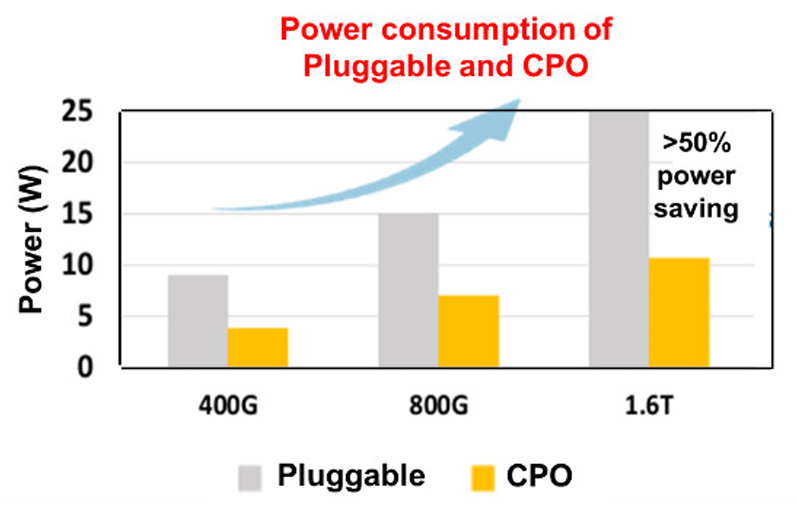

CPO 自 2023 年 Intel 与 Broadcom 出货后受到关注,将光学与电子引擎沿 ASIC 芯片四边并列于同一共封装基板。OIF 规范将 CPO 模块与主 ASIC 芯片限制于 50mm 内,通道损耗限制于 10dB。最短互连距离带来最佳电气效能。相较 NPO,CPO 在外形尺寸、功耗与延迟方面具备优势,由于较短跨距与 3dB 通道损耗减少,可节省约 50% 功耗。

图 5:可插拔与 CPO 功耗比较图,定量展示 CPO 相较传统可插拔收发模块于不同数据速率(400G、800G 与 1.6T)下的功耗节省,显示 CPO 可达成超过 50% 功耗降低。

04 各种 CPO 架构形式

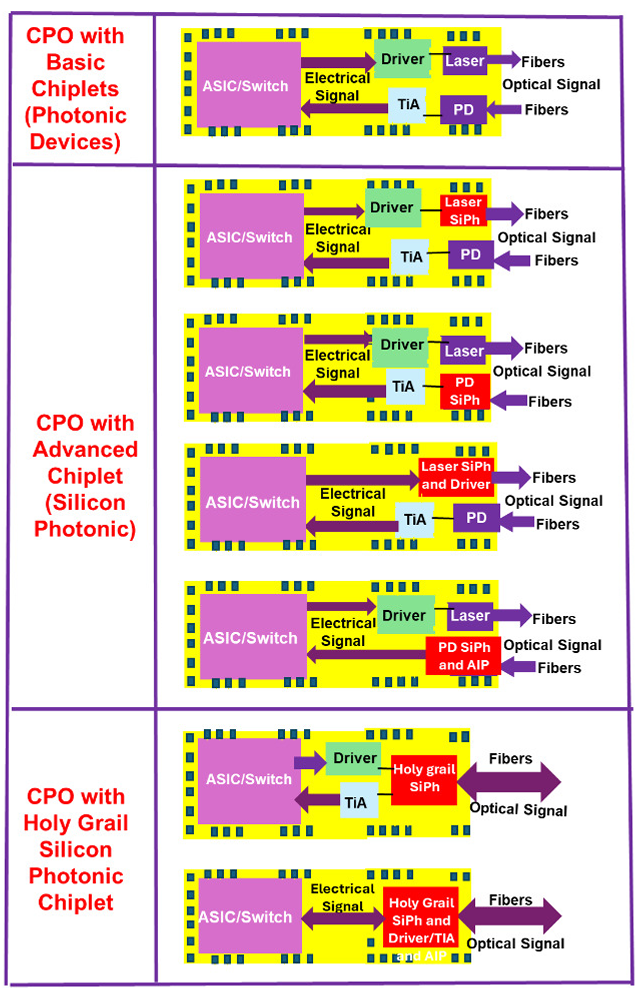

CPO 涵盖多种架构变化,各具优缺点。最常见形式采用基础 Chiplet,包括交换机、激光驱动器、TIA 与离散光电元件如激光与光检测器。此方案提供较低成本与较大弹性,但导致较大封装尺寸与较复杂的测试与老化程序。

图 6:各种 CPO 架构详细图解,呈现从基础 Chiplet 实现经进阶 Chiplet 设计(采用硅基光电子技术整合激光 / 光检测器与驱动器 / TIA 功能)到理论上完全硅基光电子整合的多种配置。

进阶变体采用硅基光电子 Chiplet 整合多项功能,例如将激光与驱动器或光检测器与 TIA 整合于单一硅芯片上,利用 CMOS 技术制造。这些进阶 Chiplet 提供较佳效能、较易测试与老化,以及较小封装尺寸,但成本较高且基础设施较为固定。理论上的终极 CPO 将所有 PIC 与 EIC 从硅晶圆透过 CMOS 技术整合至单一芯片,但此终极整合因技术与经济挑战仍未实现。

05 CPO 基板技术

CPO 实现采用各种基板技术,各适合不同效能与成本需求。硅基板采用 Through-silicon vias(TSV)Interposer 提供高性能互连与精细间距能力。玻璃基板采用激光诱导深蚀刻(LIDE)等制程,由 LPKF Laser & Electronics AG 开发,提供优异电气特性与热稳定性。有机基板为要求较低的应用提供经济有效方案。

图 7:TSV-Interposer 上 CPO 的剖面图,显示 ASIC 交换机、EIC 与 PIC Chiplet 安装于 TSV-Interposer 基板,随后安装至封装基板与印刷电路板,实现高密度互连与优异电气效能。

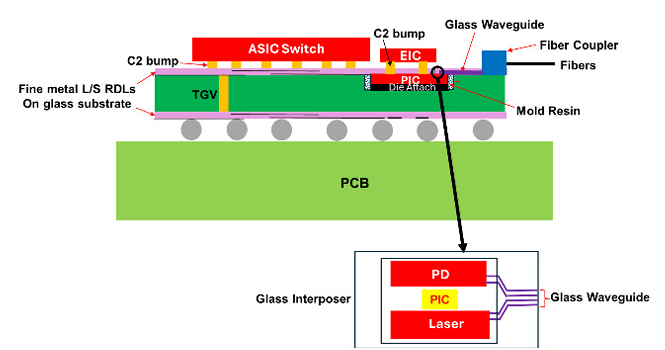

图 8:玻璃核心堆叠基板上 CPO 示意图,展示采用通玻璃孔(TGV)与光纤耦合的玻璃核心基板 CPO 实现,显示玻璃基板提供优异电气特性并实现高效率光耦合至外部光纤。

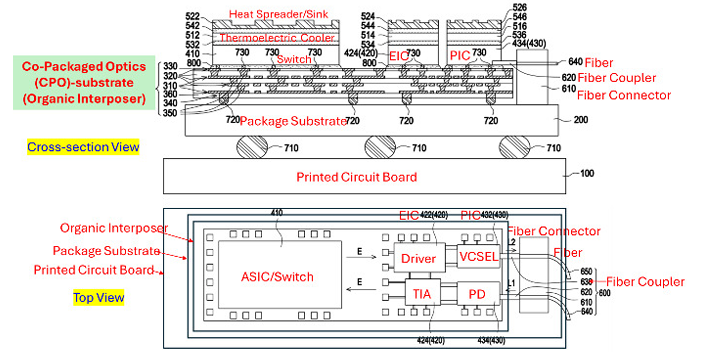

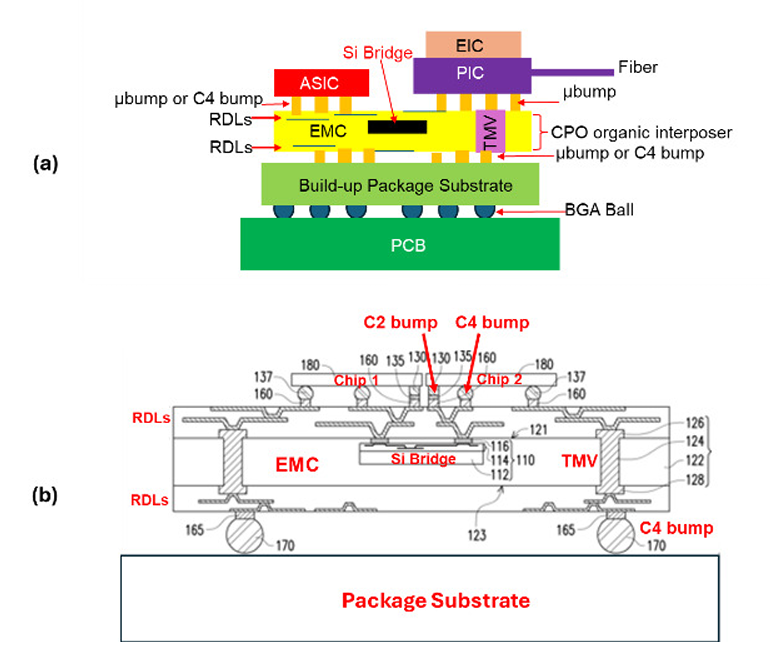

图 9:有机 Interposer 上 CPO 图示,呈现 2D 异质整合方式,ASIC 交换机芯片、EIC 芯片与 PIC 芯片并列安装,采用微凸块接合至有机 Interposer,提供 CPO 实现的经济有效方案。

06 2D 整合架构

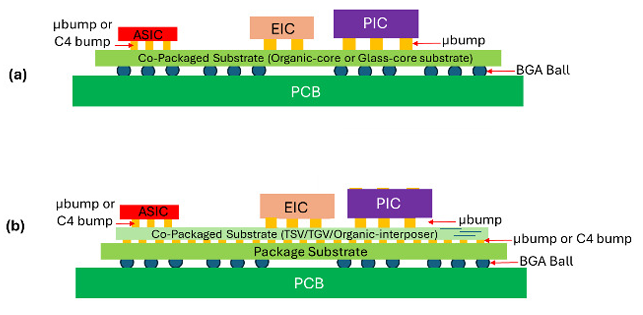

2D 异质整合将所有 Chiplet 并列于共同基板。一种配置中,ASIC 交换机、PIC 与 EIC 接合至有机核心或玻璃核心堆叠封装基板。此为适合中等效能需求的直接实现。另一方式采用 TSV-Interposer、TGV-Interposer 或有机 Interposer 作为主要基板,再接合至有机堆叠封装基板。此基于 Interposer 的配置针对较高性能应用,但成本较高。

图 10:(a) 有机核心或玻璃核心封装基板上 CPO,(b) TSV、TGV 或有机 Interposer 上 CPO,两图比较两种基础 2D CPO 架构,展示 Chiplet 可直接整合于堆叠基板或于中间 Interposer 层以增强效能。

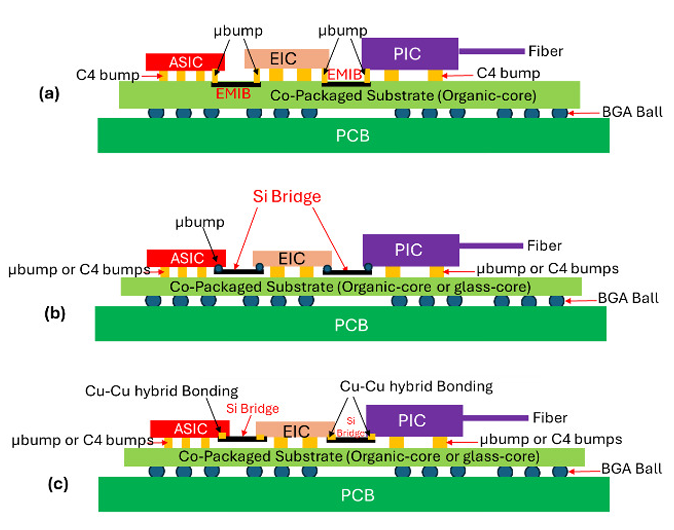

07 硅桥接技术

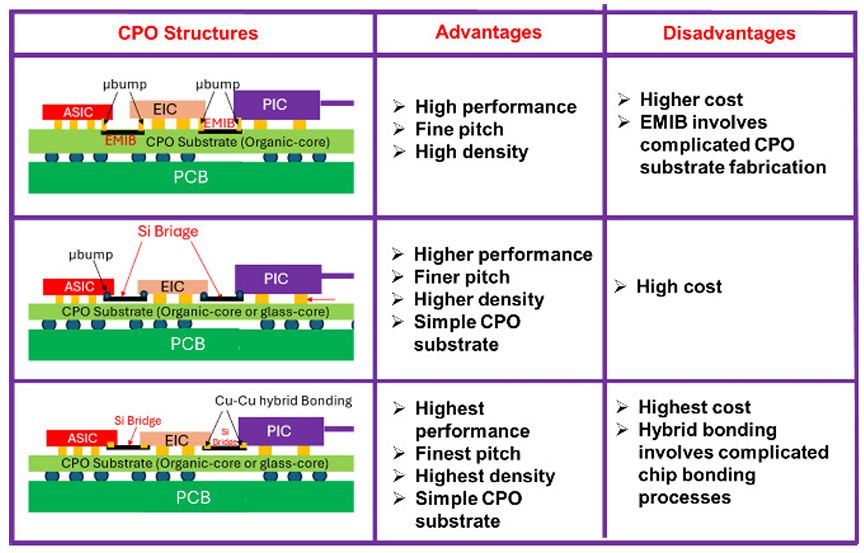

为改善 2D 配置中 Chiplet 间互连密度与效能,硅桥接提供高带宽路径。Intel 的嵌入式多晶粒互连桥接(EMIB)将硅桥接嵌入有机堆叠封装基板的凹槽内,以精细间距微凸块连接交换机至 EIC 与 EIC 至 PIC。替代方案将硅桥接置于有机核心或玻璃核心基板顶部而不嵌入,仍采用微凸块连接。最先进变体采用铜对铜(Cu-Cu)混合接合取代微凸块,消除焊料接口以达成更精细间距与更佳电气效能。

图 11:(a) 嵌入有机堆叠封装基板的 EMIB 之 CPO,(b) 玻璃核心或有机核心堆叠封装基板上芯片间采用硅桥接(微凸块)的 CPO,(c) 封装基板上芯片间采用硅桥接(混合接合)的 CPO,三部分图示展示硅桥接整合技术演进,从嵌入式桥接经表面安装桥接至混合接合桥接,各提供不同效能成本取舍。

图 12:采用桥接的各种 CPO 系统比较表,总结不同桥接整合方式的优缺点,协助系统架构师依据效能需求与成本限制选择适当技术。

08 3D 整合策略

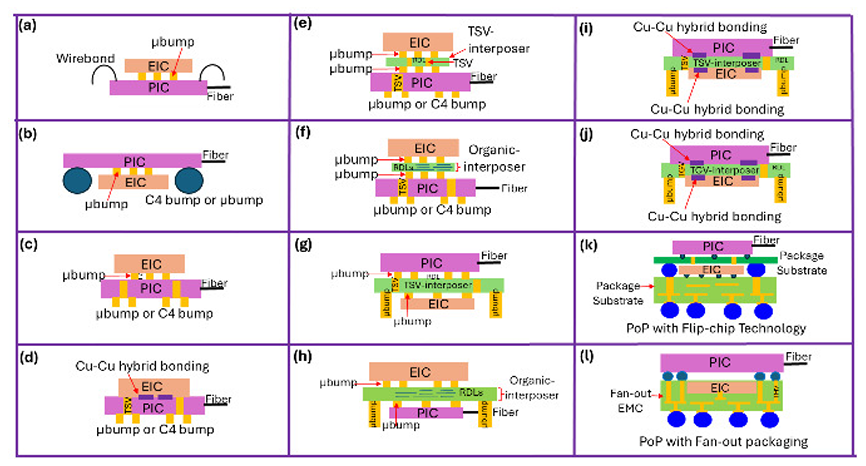

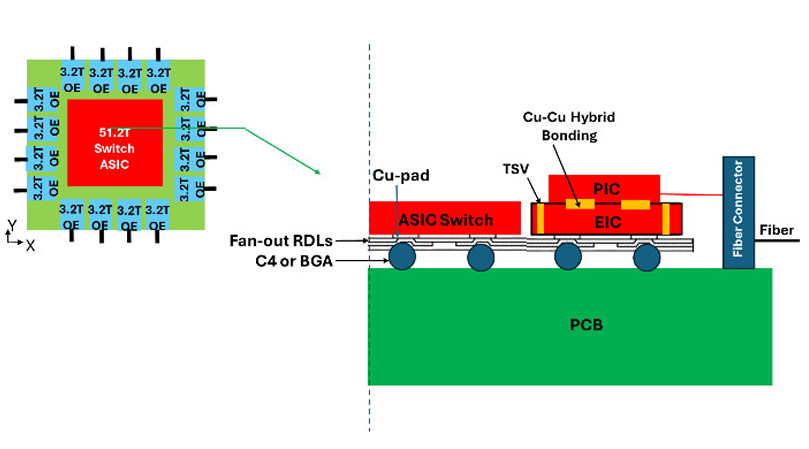

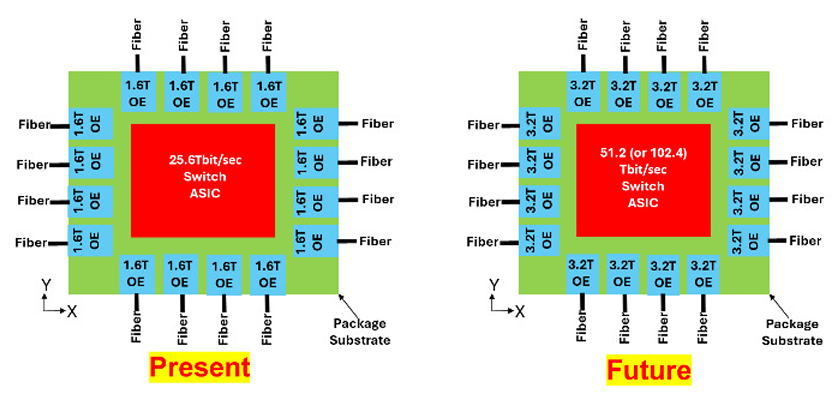

交换机芯片朝更高带宽发展,从目前需要 16 个 1.6Tbps 光学引擎的 25.6 Terabit 以太网到即将需要 3.2Tbps 引擎的 51.2 Terabit 交换机,基板上的物理空间限制变得严峻。PIC 与 EIC 元件的 3D 堆叠提供前进路径。存在多种 3D 堆叠配置,在光如何耦合至 PIC、电信号如何从堆叠芯片绕线,以及何种互连技术接合芯片方面有所差异。

图 13:各种 PIC 与 EIC 3D 堆叠示意图,呈现十种不同 3D 堆叠配置(标示 a 至 j),展示面对面与面对背堆叠的各种组合、不同互连方法(微凸块、TSV、混合接合),以及与 TSV-Interposer、TGV-Interposer 与有机 Interposer 整合。

面对面堆叠采用微凸块提供最简单 3D 整合,信号透过打线或 C4 凸块从 PIC 导出。面对背堆叠于 PIC 中整合 TSV 以绕线信号,可采用微凸块或 Cu-Cu 混合接合进行芯片对芯片连接。基于 Interposer 的堆叠于 EIC 与 PIC 间采用 TSV-Interposer、TGV-Interposer 或有机 Interposer,最先进版本于 Interposer 两侧采用 Cu-Cu 混合接合以消除所有微凸块。封装对封装(PoP)配置堆叠完整封装,一种变体对 EIC 采用焊料凸块覆晶,另一种采用扇出技术。

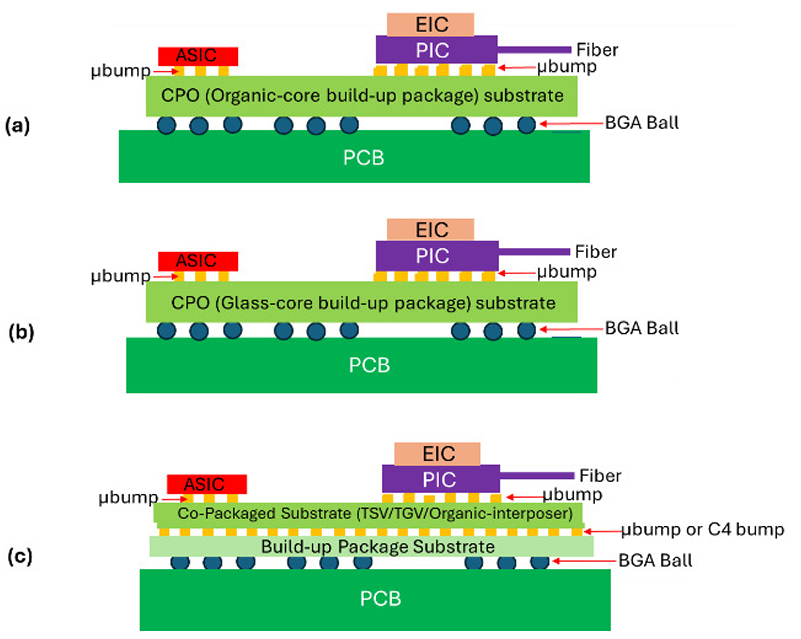

09 先进 3D CPO 架构

结合 3D 堆叠与基板整合创造高度紧凑 CPO 系统。一种实现将 3D 堆叠 PIC/EIC 模块与 ASIC 交换机并列于有机核心或玻璃核心堆叠封装基板。较高性能版本采用 TSV-Interposer、TGV-Interposer 或有机 Interposer,再接合至有机堆叠封装基板。这些 3D CPO 系统提供最大效能密度但成本较高。

图 14:(a) 有机核心封装基板上 3D CPO,(b) 玻璃核心封装基板上 3D CPO,(c) TSV、TGV 或有机 Interposer 上 3D CPO,三部分图示展示 3D 堆叠 PIC/EIC 模块如何与 ASIC 交换机于各种基板技术上整合,显示从经济有效有机基板经玻璃基板至高性能 Interposer 方案的演进。

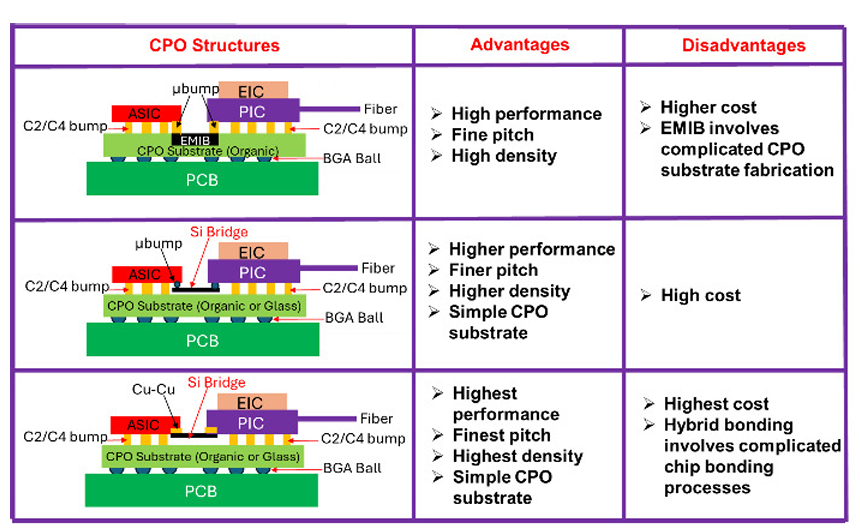

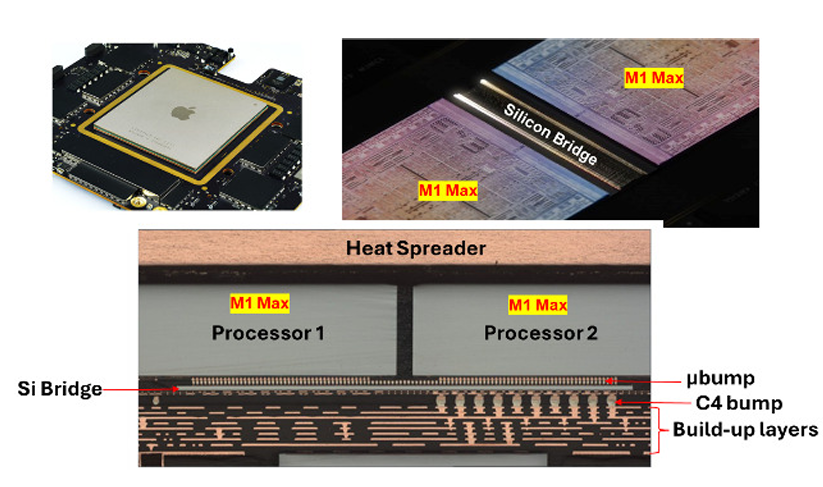

硅桥接也增强 3D CPO 架构。EMIB 技术可将桥接嵌入有机核心封装基板以连接 3D 堆叠与交换机。或者,采用微凸块或 Cu-Cu 混合接合的硅桥接可于玻璃核心或有机核心基板上连接元件而不嵌入。Apple 已于量产笔记本电脑中展示微凸块硅桥接(2022 年)与混合接合桥接(2025 年第四季),验证这些方法用于大量制造。

图 15:(a) 嵌入有机堆叠封装基板的微凸块 EMIB 之 3D CPO,(b) 有机或玻璃堆叠封装基板上采用微凸块硅桥接的 3D CPO,(c) 采用 Cu-Cu 硅桥接的 3D CPO,比较展示三种将硅桥接与 3D 堆叠元件整合的方法,突显朝混合接合演进以获最佳效能。

图 16:Intel 的 EMIB 之 CPO 照片与图示,展示 Intel 实际 CPO 实现中的 EMIB 技术于量产系统,证明嵌入式桥接方法的商业可行性。

图 17:Apple 笔记本电脑中 Chiplet 间采用微凸块硅桥接,来自 Apple 量产笔记本电脑的影像展示连接 CPU 与 GPU Chiplet 的硅桥接技术实际应用,验证该技术用于大量消费应用。

10 扇出与波导整合

扇出重布层(RDL)基板为 CPO 提供替代整合平台。这些基板将 3D 堆叠 PIC/EIC 与交换机嵌入模塑化合物中,采用 RDL 互连,简化制造同时维持合理效能。部分实现包含嵌入扇出结构的硅桥接以增强互连密度。

图 18:(a) 嵌入硅桥接的扇出 EMC 上 CPO,(b) 采用 RDL 之扇出 EMC 中嵌入硅桥接,两部分图示展示 CPO 的扇出封装方法,显示硅桥接如何整合于扇出结构内以提供 Chiplet 间高密度互连。

图 19:扇出 RDL 上 3D CPO 图示,展示于扇出 RDL 基板上实现的完整 3D CPO 系统,PIC 与 EIC 间采用 Cu-Cu 混合接合,展示简化但高性能的封装方法。

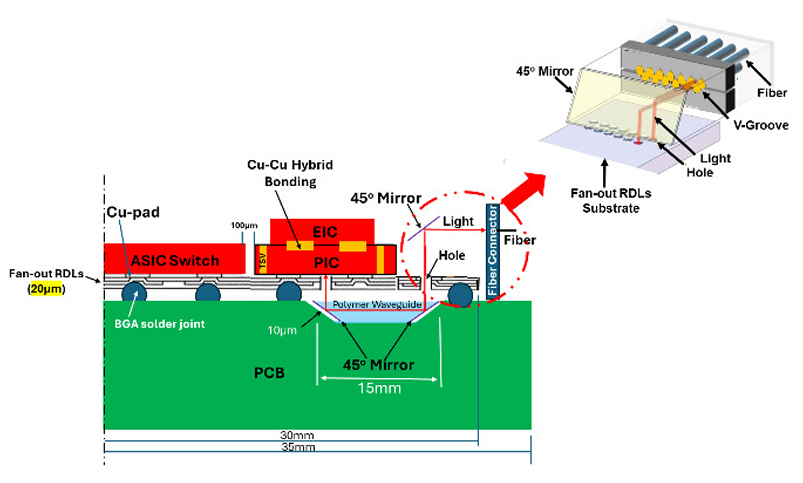

先进光耦合采用印刷电路板上聚合物波导,两端具 45 度镜面。此设计中,CPO 基板包含光通过的孔洞。外部光纤将光耦合至 V 沟槽,引导至实体镜面,将光透过基板孔洞反射至聚合物波导镜面,最终抵达 PIC 光检测器。此方法相较直接边缘耦合改善光耦合效率。

图 20:扇出 RDL 上具孔洞与印刷电路板上聚合物波导的 3D CPO 详细剖面,展示先进光耦合方案,整合 45 度镜面的聚合物波导将光从外部光纤透过扇出基板孔洞布线至 PIC 元件。

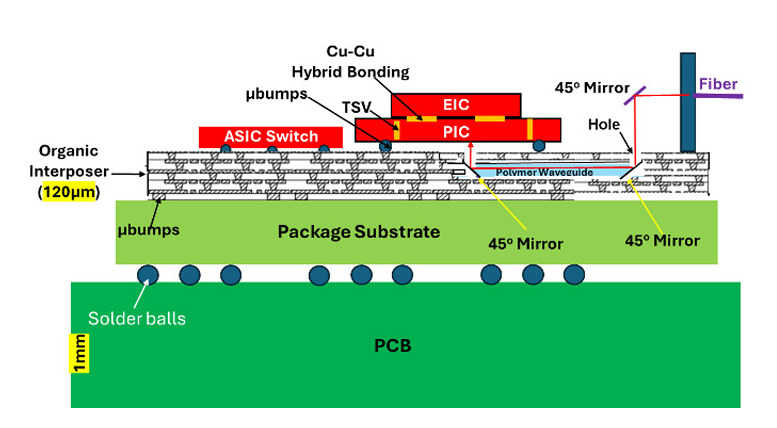

图 21:有机 Interposer 上具孔洞与嵌入聚合物波导的 3D CPO 图示,展示聚合物波导直接整合于有机 Interposer 而非印刷电路板内,创造更紧凑且潜在更高效能的光耦合方案。

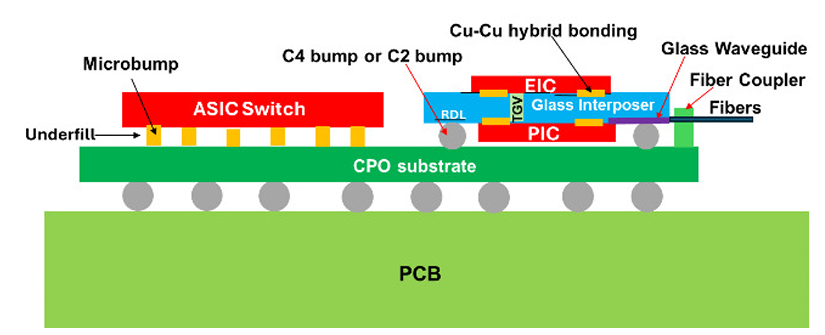

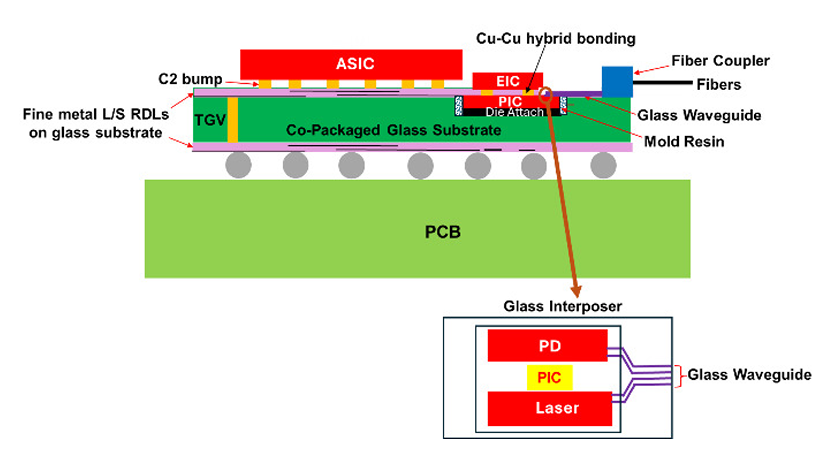

玻璃基板实现更精密光整合。具 TGV 与整合玻璃波导的玻璃 Interposer 可直接于基板内布线光信号。一种配置中,3D 堆叠 PIC/EIC 透过包含具 45 度镜面玻璃波导的 TGV-Interposer 连接,整个组件接合至堆叠封装基板与印刷电路板。此提供优异光学与电气效能于紧凑外形尺寸。

图 22:TGV Interposer 堆叠的 3D CPO 剖面图,展示具 TGV 与整合玻璃波导的玻璃 Interposer 如何创造高度整合 CPO 模块,具备优异光布线能力。

图 23:半嵌入玻璃核心基板的 3D CPO 示意图,展示先进封装方法,3D 堆叠 PIC/EIC 部分嵌入玻璃核心基板凹槽内,最大化整合密度同时促进光耦合。

11 高效能运算整合

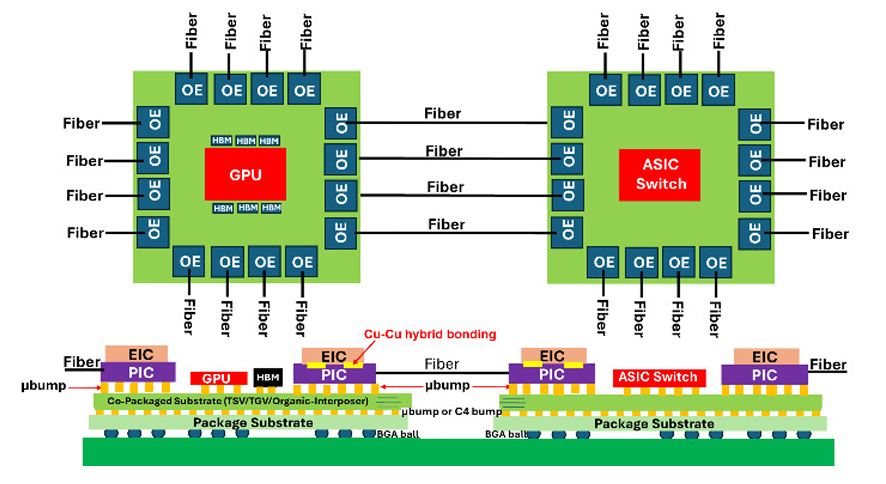

针对 AI 驱动高性能运算与高带宽通讯,CPO 架构将处理单元环绕光学引擎。一种配置将 GPU 环绕高带宽内存(HBM),光学引擎配置于此核心周围。另一种配置 ASIC 交换机环绕光学引擎。两种架构中,PIC 与 EIC 采用 Cu-Cu 混合接合的 3D 堆叠,整个组件整合于 TSV-Interposer、TGV-Interposer 或有机 Interposer 后接合至印刷电路板。

图 24:GPU、HBM、交换机、PIC 与 EIC 用于 AI 驱动高性能运算与高速高带宽通讯的 3D 异质整合系统层级图,展示完整 AI 加速器模块,显示配备 HBM 的 GPU 与 ASIC 交换机如何与多个 3D 堆叠光学引擎于先进 Interposer 基板上整合,代表当前 CPO 技术顶峰。

12 总结与未来方向

光电共封装代表数据中心互连技术的发展方向。透过将光学与电子引擎直接与交换机 ASIC 整合于共同基板,CPO 相较传统可插拔收发模块在功耗、延迟与外形尺寸方面达成显著降低。此技术涵盖从采用离散 Chiplet 的经济有效的有机基板到采用整合波导与 3D 堆叠硅基光电子元件的先进玻璃 Interposer 的一系列实现。

图 25:现在与未来 CPO 系统前瞻图,比较目前配备 16 个 1.6Tbps 光学引擎的 25.6Tbps CPO 实现与需要 16 个 3.2Tbps 引擎的未来 51.2Tbps 系统,展示驱动 3D 整合与先进封装技术的扩展挑战。

展望未来,数个发展将形塑 CPO 演进。质量与可靠性数据仍然稀少,几乎没有 CPO 组件热循环、机械冲击或加速老化特性的公开研究。3D CPO 结构的热管理呈现需要创新方案的挑战。玻璃基板与 Interposer 为未来系统提供路径,提供优异电气特性结合整合光布线能力。随互连密度需求增长,Cu-Cu 混合接合将变得更加必要,实现更精细间距连接与优异电气与热效能。产业也必须处理光泄漏问题,包括耦合损耗、波导裂纹、散射与吸收,若未妥善管理可能成为可靠性疑虑。随交换机带宽持续扩展超越 100Tbps,3D 异质整合、先进基板与混合接合技术的结合将是满足下一代 AI 基础设施与数据中心网络需求的必要条件。

参考文献

[1] J. H. Lau, "Co-Packaged Optics - Heterogeneous Integration of Chiplets (Switch, Photonic IC, and Electronic IC)," Journal of Microelectronics and Electronic Packaging, vol. 22, no. 4, pp. 93-104, 2025. https://doi.org/10.4071/001c.154275

来源:《逍遥设计自动化》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。