高速电镀铜入门精要

一、概述

在FCBGA、扇出型封装、WLP、SiP、2.5D/3D封装、Chiplet等先进封装形式中,关键技术主要包括再布线、凸点、硅通孔、晶圆重构、临时键合与解键合、混合键合等。这些工艺技术的核心目标是通过多种金属互连结构的组合,将单颗或多颗芯片的电极端口引出至封装体表面,形成可与外部电路连接的球栅阵列,进而实现完整的系统功能。因此,先进封装中的各项工艺本质上是为实现多样化、高密度的金属互连而发展起来的。

在各类互连结构中,铜凭借其优异的电学和机械性能成为应用最广泛的金属材料。当前主流的RDL、凸点、TSV及混合键合技术大多以铜作为核心互连金属。早期因铜的熔点较高,铜-铜直接键合较为困难,多通过锡金属实现电气连接。随着混合键合技术的发展,目前已能在实验条件下实现约200℃的铜/介电层混合键合。

铜互连结构的制备主要有化学镀铜和电化学镀铜两种方法。化学镀铜虽具有镀层平整度高、孔隙率低的优点,但其沉积速率低、镀液寿命短,限制了其大规模应用。因此,电化学沉积仍是目前主流的铜层制备工艺。

电镀铜是一项综合性强的复杂工艺,其沉积速率受多类因素影响,主要包括:

1.原材料因素:如电镀液成分、添加剂种类与含量及其协同效应;

2.工艺环境因素:涉及电流均匀性、温度、对流传质条件等,主要由电镀设备控制;

3.工艺控制因素:通过选择与优化电镀参数,可在保证镀层质量的同时实现较高的沉积速率。

二、核心应用场景

高速电镀铜技术是现代先进封装中的“骨架构建者”,它并非制造单一的连接点,而是通过精密的电化学沉积,直接在硅晶圆或中介层上构筑出承担电气连接、机械支撑和热传导功能的复杂三维金属互连网络。其主要应用聚焦于以下三种核心互连结构的制造,每种结构都对应着独特的工艺挑战与技术突破。

2.1 铜柱凸点 (Copper Pillar Bump, CPB)

铜柱凸点是倒装芯片(Flip-Chip)技术的核心互连单元,用于替代传统的锡铅焊球,实现芯片与基板之间的直接、高密度电气和机械连接。

· 结构特征:典型的铜柱呈圆柱体状,具有高深宽比(高度通常在30-100μm,直径30-60μm,深宽比可达1.5:1至2:1)。其顶端会覆盖一层薄薄的锡银(SnAg)焊料盖帽,以利于后续的回流焊接。

· 工艺挑战与高速电镀解决方案:

1.挑战一:形貌与均匀性控制。数千乃至数万个铜柱必须在整个晶圆上保持高度和直径的高度一致性,否则会导致键合时受力不均,产生“虚焊”或“桥连”。

解决方案:高速电镀通过 “整平剂(Leveler)”添加剂和优化的脉冲电镀波形,有效抑制高电流密度区域的过快生长(如铜柱顶部边缘),确保垂直生长和顶部平坦。

2.挑战二:高深宽比下的无缺陷填充。虽不及TSV极致,但较高的深宽比仍需避免内部空洞。

解决方案:利用 “加速剂(Accelerator)” 在铜柱底部凹处的优先吸附和催化作用,结合强制对流,实现自下而上的超填充(Bottom-up Superfilling)。

2.2 硅通孔 (Through-Silicon Via, TSV)

硅通孔是2.5D/3D集成封装(如CoWoS、HBM高带宽内存)的“垂直电梯”,是实现芯片间垂直堆叠与最短互连路径的关键。

· 结构特征:在硅衬底上刻蚀出的垂直通孔,深宽比极高(孔径5-10μm,深度50-100μm,深宽比可达10:1以上)。孔内需完全填充高纯度铜,以实现低电阻的垂直导电通道。

· 工艺挑战与高速电镀解决方案:

1.挑战一:无缝隙/空洞的超填充。这是TSV电镀的核心难题。若采用常规电镀,孔口会因电流密度高而快速封口,在孔中心留下致命的缝隙或空洞。

解决方案:这正是添加剂协同作用的经典体现。“抑制剂(Suppressor)”(如PEG)在孔口和平面区域形成强吸附层,大幅减缓此处的沉积速度;同时,“加速剂”(如SPS)分子小,扩散快,能渗透至孔底并优先吸附,在孔底“开启”快速沉积模式,从而实现从底至顶的完美填充。

2.挑战二:热机械应力管理。铜与硅的热膨胀系数差异巨大,填充后的TSV在温度循环中会对周围硅产生巨大应力,可能引发硅裂纹或晶体管性能漂移。

解决方案:通过电镀后的低温退火工艺,调整铜的晶粒结构和应力状态。优化电镀参数以生成更细密、应力更低的铜晶粒。

2.3 再布线层 (Redistribution Layer, RDL)

再布线层是先进封装的“内部交通网”,特别是扇出型(Fan-Out)和晶圆级封装(WLP)的关键技术。它将芯片上密集、精细的I/O焊盘,重新布局并“扇出”到更适于与外部互连的、节距更大的位置。

· 结构特征:由沉积在晶圆表面的多层、超细的铜互连线构成。线宽/线距已进入亚微米级(例如,当前先进节点已达到<2μm,并正向<1μm迈进)。

· 工艺挑战与高速电镀解决方案:

1.挑战一:超细线宽下的均匀性与保形性。在微米级沟槽内沉积铜,必须保证整个晶圆上所有线条的厚度、宽度和电阻均匀一致,且不能有过多的“过镀”(Overburden)。

解决方案:依赖于高度平衡的添加剂体系和精密的设备设计。通过整平剂实现优异的平面化能力,确保沉积后的铜表面尽可能平坦,为后续的化学机械抛光(CMP)减轻负担。同时,高均匀性的电流分布和晶圆级流场设计是关键。

2.挑战二:低电阻率与高可靠性。沉积的铜膜电阻率需尽可能接近体铜(1.68 μΩ·cm),以保证信号完整性。同时,细线条需承受电流密度考验。

解决方案:优化电镀液基本成分(硫酸铜、硫酸)和有机添加剂的比例,并使用脉冲反向(PR)电镀来细化晶粒、减少杂质夹杂,从而获得低电阻率、高抗电迁移能力的致密铜膜。

总结而言,高速电镀铜技术通过一套精密的“物理-化学-电气”协同控制系统,为先进封装量身定制了从垂直互连(TSV)、点对点互连(CPB) 到平面互连(RDL) 的完整“铜骨架”解决方案。理解这三种结构的制造需求,是掌握高速电镀铜技术价值与难点的基石。

电镀铜在先进封装中的应用

Application of copper electroplating in advanced packaging

2.5D硅转接板TSV工艺流程

TSV process flow of 2.5D silicon interposer

三、技术内核

高速电镀铜的本质是在保持镀层质量的前提下,大幅提升沉积速率。这依赖于对电化学沉积过程的精准控制,主要体现在物理传质强化和化学添加剂调控两个层面。

3.1 “高速”的实现:强化传质与精准控制

1.高电流密度驱动

· 常规电镀电流密度:1-10 mA/cm²

· 先进封装电镀电流密度:可达20-80 mA/cm²

· 沉积速率提升:从常规的0.1-0.5 μm/min提升至1-3 μm/min

2.强制对流系统设计

· 喷淋式流场:通过精密设计的喷头阵列,使电镀液以3-10 m/s的速度垂直冲击晶圆表面

· 旋转盘电极系统:晶圆高速旋转(100-500 rpm),产生离心力加速传质

· 湍流控制:精确控制边界层厚度至10-50 μm,确保离子供应充足

3.脉冲电镀技术

· 正向脉冲:高电流密度下沉积(10-100 ms)

· 反向脉冲:短时间溶解(1-5 ms),去除不良沉积

· 间歇时间:允许添加剂重新分布(5-20 ms)

优势:实现纳米级表面平整,减少孔口封堵风险

3.2 “添加剂”的协同魔法

添加剂的协同作用机制类似键合铜丝中的微量元素掺杂,但在液固界面进行动态调控:

1.协同作用动态过程

· 孔底优先填充机制:加速剂小分子快速扩散至深孔底部,局部降低沉积电位

· 孔口抑制效应:大分子抑制剂在孔口形成阻挡层,延缓沉积

· 自平整功能:整平剂在凸起处吸附,实现表面平坦化

2.实时监控与反馈

在线电化学监测:通过CV、EIS等技术实时监测添加剂消耗

光学终点检测:利用激光干涉测量沉积厚度

自动补液系统:根据监测数据自动补充添加剂

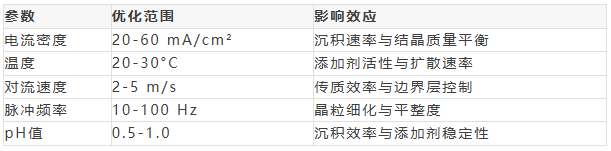

3.3 工艺参数优化窗口

3.4 先进技术演进

1.超声辅助电镀

· 频率:20-100 kHz

· 作用:微空化效应增强传质,细化晶粒

2.磁场辅助电镀

· 场强:0.1-1.0 T

· 作用:洛伦兹力改变沉积取向,改善填充特性

3.多物理场耦合

· 热-流-电-化多场协同

· 实现亚微米级形貌控制

技术核心总结:高速电镀铜通过“物理强化传质”实现高速沉积,通过“化学添加剂协同”保证镀层质量。这种“硬实力+软调控”的组合,使其能够满足先进封装对互连结构在速率、精度、可靠性方面的严苛要求,成为替代传统键合技术的关键工艺。

四、总结

高速电镀铜技术是先进封装金属互连制造的核心工艺,通过精密控制电化学沉积过程,在硅晶圆或中介层上直接构筑三维铜互连结构。该技术成功解决了铜柱凸点、硅通孔和再布线层等关键结构的制造难题:通过高电流密度驱动(20-80 mA/cm²)和强制对流系统实现快速沉积;利用抑制剂、加速剂和整平剂的协同作用,实现无空洞的超填充和优异形貌控制;配合脉冲电镀技术获得纳米级表面平整度。这些创新使电镀铜能够满足2.5D/3D封装、扇出型封装等对高密度互连的严苛要求,在沉积速率、填充质量和可靠性方面均超越传统化学镀铜,成为替代键合铜丝的主流技术方案,为摩尔定律延续提供了关键的互连解决方案。

来源:《芯禾叶带你看芯片》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。