晶圆的"边缘困境":为什么同样的沙子,命运却天差地别?

想象一下,你走进一家米其林餐厅,点了一份招牌牛排。厨师用同一块牛肉、同样的手法、同样的温度煎制,但最后端上来的两块牛排——一块鲜嫩多汁,堪称完美;另一块却干柴僵硬,难以入口。这听起来像是玄学,但在半导体世界,这却是每天都在上演的真实故事。

故事的主角,是一片直径30厘米以内的圆形硅片——晶圆。

01 同样的起点,不同的终点

在芯片制造的世界里,晶圆就像是芯片的"庄稼地"。一粒沙子(高纯度硅)被熔炼成单晶硅锭,再切割成薄如蝉翼的圆片,经过数百道精密工序的"精雕细琢",最终变成我们手机、电脑里那颗强大的"大脑"——芯片。

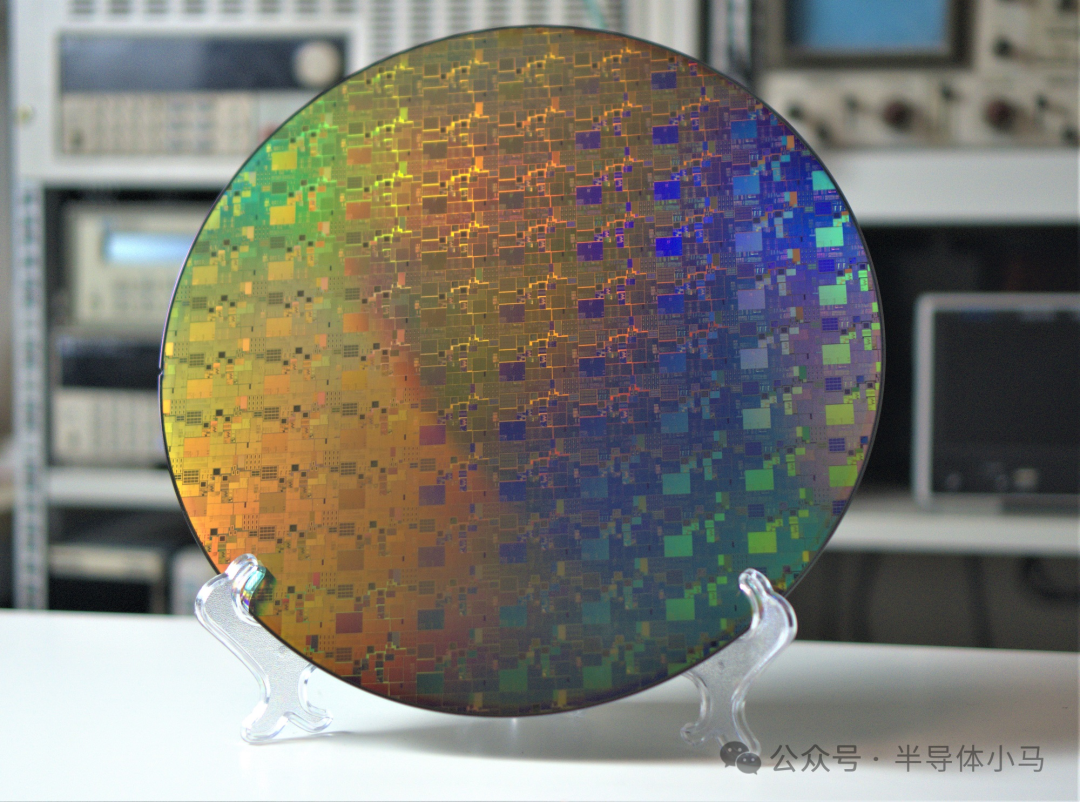

图1:一片硅晶圆,表面布满整齐排列的芯片阵列,在光线照射下呈现出绚丽的色彩

但有趣的事情发生了:同一片晶圆上"生长"出来的数百颗芯片,它们的命运却截然不同。位于晶圆中心的芯片,往往性能卓越、质量可靠,是厂商眼中的"优等生";而位于晶圆边缘的芯片,则可能出现各种问题——性能不达标、功耗过高、甚至直接报废。

这种神奇的现象,有一个专有名词:晶圆边缘效应(Wafer Edge Effect)。

02 什么是晶圆边缘效应?

用一个生活中的类比来解释:想象你在一个圆形的泳池里学游泳。泳池中央的水温恰到好处,水流平稳,适合畅游;但靠近池边的区域,由于与池壁的碰撞、水流的折射,温度和流速都会发生变化,甚至可能让你呛水。

晶圆的情况与此类似。

晶圆中心区域就像泳池中央的"黄金地带",各种工艺条件——光刻机的光源、沉积反应的气流、等离子体的轰击——都能以最均匀、最稳定的方式作用于这片区域。而晶圆的边缘区域,则像泳池边缘一样,充满了各种"不稳定因素":

1. 光刻的"失焦"困境

光刻是芯片制造中最关键的"画笔"——它把设计好的电路图案精确地"印刷"到晶圆上。但光刻机存在一个天然的"视场限制":中心区域光线均匀、聚焦精准,而边缘区域容易出现离焦和图形失真。

更糟糕的是,在涂布光刻胶时,边缘区域因表面张力的作用,会形成一种叫做"边缘珠状效应"(Edge Bead)的现象——光刻胶在边缘堆积或变薄,导致显影后图形残缺、线宽偏移,严重时甚至造成电路短路或开路。

图2:晶圆制造过程中,机械装置精密夹持晶圆进行操作

2. 温度的"冷热不均"

芯片制造涉及大量高温工艺,如薄膜沉积、退火、氧化等。晶圆中心被温控系统"温柔"地包裹着,温度分布均匀;而边缘区域则像被遗忘在暖气片角落的花盆——散热更快、温度更低,形成明显的热应力梯度。

这种冷热不均会导致什么问题呢?想象一下,把一块巧克力从冰箱突然放进烤箱——它会因为热胀冷缩不均而碎裂。晶圆边缘的硅材料也是如此,热应力会诱发晶格缺陷和微观裂纹,影响芯片的可靠性。

3. 气流的"边界效应"

在薄膜沉积(如 CVD、PVD)和等离子刻蚀过程中,反应气体的流动和等离子体的分布都需要高度均匀。但晶圆边缘是气流的"终点",气流扩散速度更快、等离子体密度更不稳定。

结果是:边缘区域的薄膜厚度可能出现超过 7% 的偏差,刻蚀时也可能出现过刻或欠刻的问题。这些微小的偏差,在纳米级的芯片世界里,足以让晶体管"性格大变"。

4. 污染的"垃圾场"

晶圆的边缘像城市里的"城乡结合部"——各种颗粒污染物、有机残留物都喜欢在这里"安营扎寨"。统计数据显示,边缘区域的颗粒污染密度比中心区域高出 20%~30%。

这些污染物可能在光刻时造成遮挡,在薄膜沉积时引入杂质,成为芯片失效的"定时炸弹"。

图3:半导体制造洁净室内的工作场景,工作人员身着全包式洁净服

03 边缘效应如何"蚕食"良率?

说了这么多,边缘效应到底如何影响晶圆的良率(Yield)——即合格芯片占总芯片的比例?

让我们看一组数据:

以 28nm 工艺为例,边缘 Die 的漏电平均比中心高 30%,良率低 8%~12%。而晶圆边缘区域(外部 10mm 范围)可能包含多达 10% 的芯片——这意味着,如果不做任何处理,晶圆有超过十分之一的产能会被边缘效应"吞噬"。

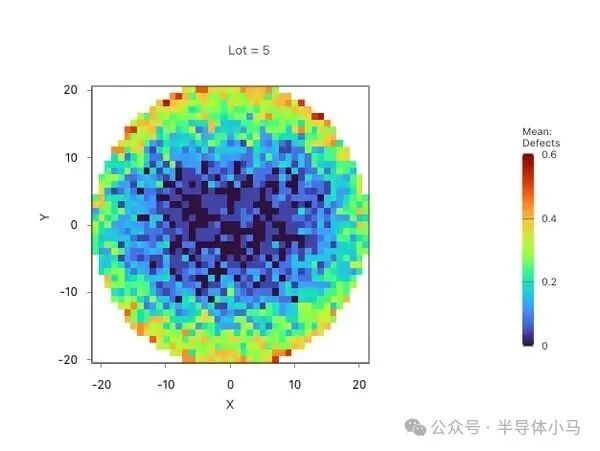

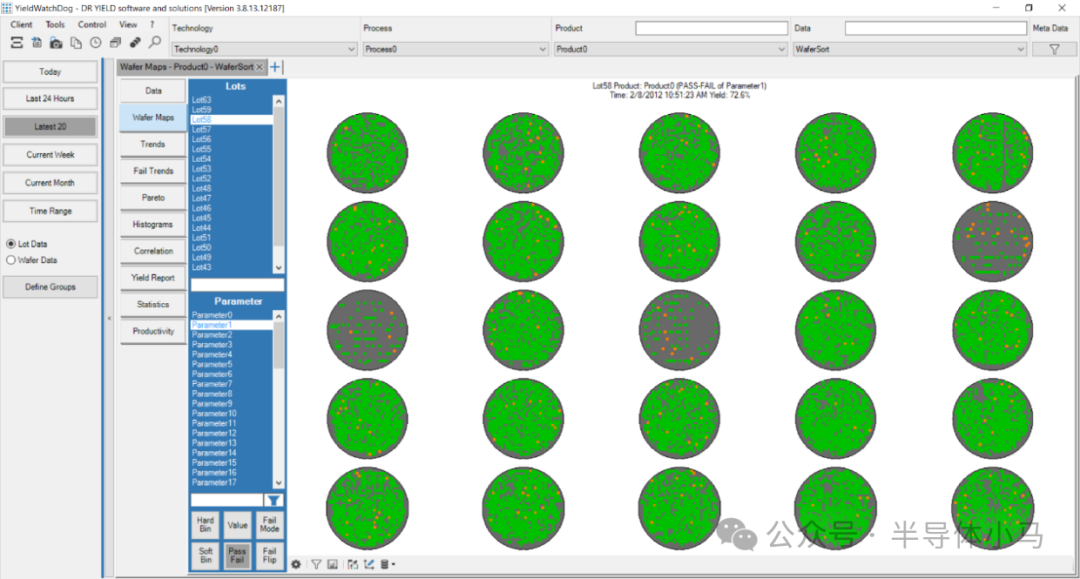

晶圆良率分布图

下面是一张真实的晶圆良率分布图(Wafer Map),可以清晰地看到边缘效应的影响:

图4:晶圆边缘形成红色环形缺陷区域,这通常是快速热退火过程中温度分布不均的典型表现

这张图来自实际生产数据,红色区域表示缺陷芯片。可以明显看到,晶圆边缘形成了一个完整的"红色环"——这正是边缘效应的直观体现。这种环形缺陷模式通常指向温度控制问题,工程师据此可以快速定位到快速热退火(RTP)工艺环节。

再看另一组晶圆测试数据:

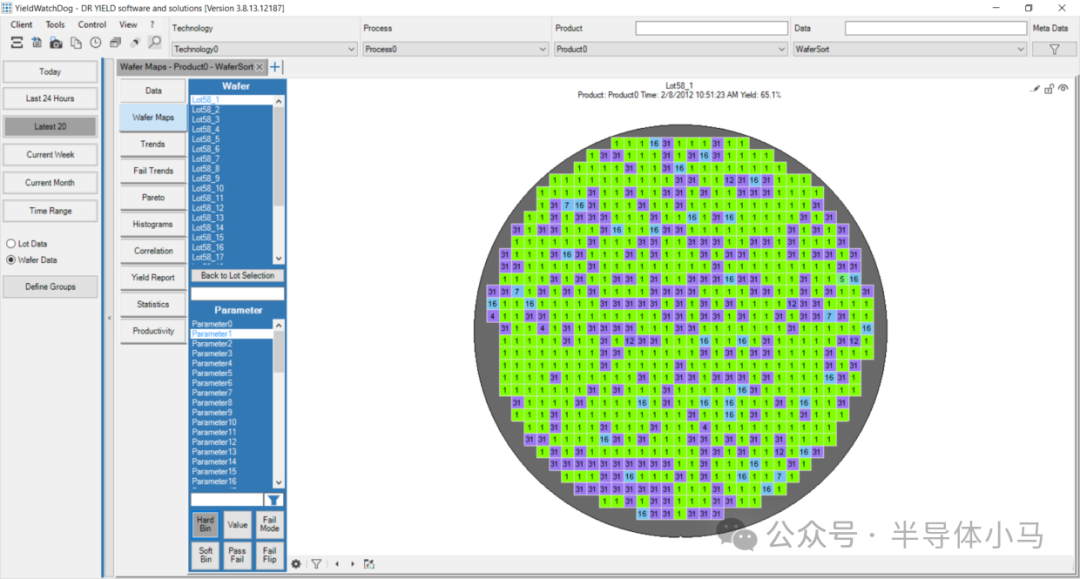

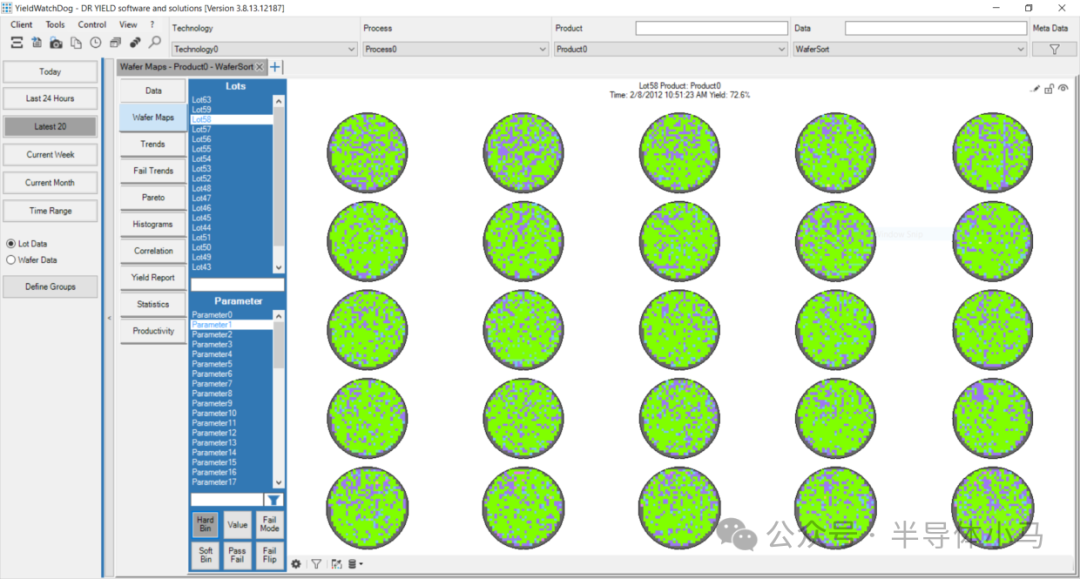

图5:晶圆测试结果Bin Map,不同颜色代表不同的测试结果类别

图6:多个批次晶圆的测试结果对比,边缘区域失效模式明显

通过多批次对比,工程师可以识别出哪些缺陷是系统性的(每个批次都出现),哪些是随机性的。边缘区域的缺陷往往呈现系统性特征。

图7:晶圆通过/失效分布图,橙色标记失效芯片

04 行业如何破局?

面对边缘效应这个"拦路虎",半导体行业并没有坐以待毙,而是发展出了一套多维度的应对策略。

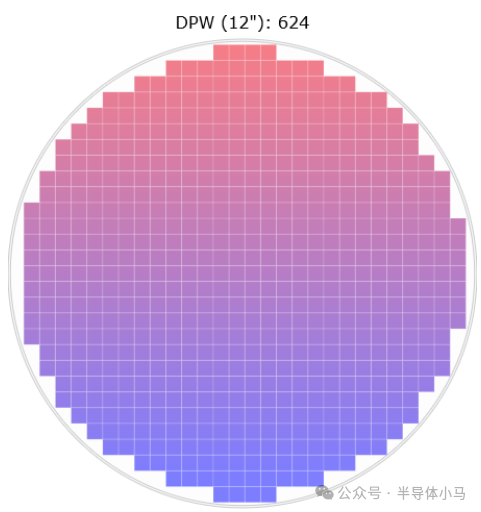

策略一:边缘排除(Edge Exclusion)—— 壮士断腕

最直接的策略是划定"楚河汉界":在晶圆最外围 3~5mm 处设定边缘排除区,这片区域内的芯片直接被判定为"非有效区域",不参与正常生产。

这个策略看似"浪费"——毕竟白白舍弃了晶圆边缘的芯片产能。但事实上,这是兼顾成本与质量的最优选择:通过牺牲少量边缘芯片,换取中心区域高良率的稳定输出,避免边缘劣质芯片流入下游,造成更大的损失。

图8:晶圆上芯片(Die)分布示意图,边缘区域通常被排除在有效产能之外

策略二:工艺优化—— 精准调控

光刻环节:引入边缘曝光校正技术,优化光刻胶涂布的边缘控制算法,减少边缘珠状效应

沉积环节:改进设备的气流场和温度场设计,采用分区控温、边缘气流补偿等技术

刻蚀环节:调整等离子体功率分布、优化离子束扫描路径,改善边缘均匀性

策略三:设备升级 —— 硬件加持

聚焦环(Focus Ring):填补晶圆边缘与电极之间的高度差,使等离子体鞘层更加平坦,确保离子垂直轰击晶圆表面

可调间隙技术:在电容耦合等离子体(CCP)腔体中,通过调整极板间距优化离子通量分布

分区温控:从单区、双区、四区,发展到如今的 100+ 温控区域,实现纳米级的温度精度控制

策略四:AI 赋能 —— 智能检测

引入 AI 辅助检测算法,对晶圆图像进行实时分析,自动识别边缘区域的微小缺陷,提升检测效率和准确率,减少漏检和误判。

边缘芯片的"人生规划"

即便采取了上述措施,边缘区域仍会有部分芯片"幸存"下来。这些芯片虽然不如中心芯片"品学兼优",但经过严格测试和筛选后,仍然可以发挥余热:

降级使用:被筛选为低频版、低功耗版,用于对性能要求不高的场景,如低端消费电子、普通工业控制

特殊用途:某些对参数离散度要求不高的模拟芯片,可以在边缘找到自己的"用武之地"

这也是为什么同一款手机处理器,会有"满血版"和"残血版"之分——它们可能来自同一片晶圆,却因为"出生地"的不同,走上了不同的"人生道路"。

05 未来:挑战与机遇并存

随着半导体工艺节点不断演进到 3nm、2nm 甚至更先进的尺度,晶体管尺寸逼近物理极限,边缘效应带来的挑战愈发严峻:

允许的工艺变异越来越小(5nm 节点下可能低于 0.5nm,仅相当于 2~3 个硅原子的厚度)

边缘区域的任何微小偏差,都可能被无限放大,直接导致芯片失效

但挑战与机遇并存。新型材料(如碳纳米管、第三代半导体)、Chiplet 架构(将大芯片拆分为小芯粒,降低单芯片面积)、AI 驱动的智能制造,都有望从根本上缓解边缘效应带来的影响。

06 一沙一世界,边缘见真章

回到文章开头那个牛排的类比。同样的食材、同样的厨师、同样的烹饪,却产生了截然不同的结果——这背后是物理规律的使然,是工程艺术的权衡,更是人类智慧与极限的较量。

晶圆边缘效应,表面上是半导体制造中的一个技术难题,实则折射出更深层的哲学命题:在追求极致完美的道路上,边界与限制往往才是创新的真正起点。

当我们站在 2026 年的今天,回望过去几十年半导体产业的发展历程,从微米到纳米、从 180nm 到 2nm,每一次突破都伴随着对"边缘困境"的重新定义与突破。也许在不久的将来,晶圆的每一个角落都能成为"黄金地带",每一颗芯片都能达到同等卓越的性能。

但在那之前,边缘效应仍将是我们理解半导体制造、理解工程极限的一扇重要窗口。

来源:《半导体小马》

免责申明:文章版权归原作者所有,如您(单位或个人)认为内容有侵权嫌疑,敬请立即通知我们,我们将第一时间予以更改或删除。